# **amu** AS8580

## **Datasheet**

## **Table of contents**

| 1 | Gen  | eral description                               | 5  |

|---|------|------------------------------------------------|----|

|   | 1.1  | Key benefits & features                        | 6  |

|   | 1.2  | Application example                            | 6  |

|   | 1.3  | Block diagram                                  | 7  |

| 2 | Ord  | ering information                              | 8  |

| 3 | Pac  | kage                                           | 8  |

|   | 3.1  | Pin description                                | 9  |

| 4 | Abs  | olute maximum ratings (non-operating)          | 10 |

| 5 | Elec | trical characteristics                         | 11 |

|   | 5.1  | Operating conditions                           | 11 |

|   | 5.2  | DC/AC characteristics for inputs and outputs   | 12 |

|   | 5.3  | Internal ESD protection concept                | 14 |

| 6 | Fun  | ctional description                            | 16 |

|   | 6.1  | Operation modes overview                       | 17 |

|   | 6.2  | Generate trigger mode                          | 19 |

|   | 6.3  | Wait mode                                      | 19 |

|   | 6.4  | Initialization mode                            | 19 |

|   | 6.5  | Single measurement mode                        | 20 |

|   | 6.6  | Continuous measurement mode                    | 22 |

|   | 6.7  | Polling measurement mode                       | 24 |

|   | 6.8  | Low power mode                                 | 27 |

|   | 6.9  | Diagnostic modes                               | 27 |

|   | 6.10 | Diagnostic features                            | 29 |

|   | 6.11 | Measurement sequence with configuration tables | 30 |

|   | 6.12 | Chip ID                                        | 31 |

|   | 6.13 | SPI interface                                  | 31 |

|   | 6.14 | SPI timing characteristics                     | 34 |

| 7 | Deta | ailed system and block specification           | 35 |

|   | 7.1  | System timing                                  | 35 |

|   | 7.2  | System parameters                             | 36 |

|---|------|-----------------------------------------------|----|

|   | 7.3  | PLL                                           | 37 |

|   | 7.4  | TX sine DAC / filter                          | 38 |

|   | 7.5  | TX driver and current sensing                 | 38 |

|   | 7.6  | TX multiplexer                                | 38 |

|   | 7.7  | Trans impedance amplifier                     | 38 |

|   | 7.8  | Band pass filter / pre-amplifier              | 39 |

|   | 7.9  | Demodulation                                  | 39 |

|   | 7.10 | Low pass filter                               | 39 |

|   | 7.11 | Offset comp: Programmable gain amplifier      | 39 |

|   | 7.12 | ADC                                           | 39 |

|   | 7.13 | Voltage regulators                            | 40 |

|   | 7.14 | Supply monitor                                | 40 |

| 8 | SW i | interface                                     | 41 |

|   | 8.1  | MEMT DATA 1-16 (Address 0x00-0x0F, all banks) |    |

|   | 8.2  | BANK SEL (Address 0x10, all banks)            |    |

|   | 8.3  | MEMT SEQ (Address 0x11, bank 0)               |    |

|   | 8.4  | MEMT CNTL 1 (Address 0x12, bank 0)            |    |

|   | 8.5  | MEMT CNTL 2 (Address 0x13, bank 0)            |    |

|   | 8.6  | MEMT_CNTL_3 (Address 0x14, bank 0)            |    |

|   | 8.7  | POLL CYC CNT (Address 0x15, bank 0)           |    |

|   | 8.8  | POLL_CYC_CNT_STS (Address 0x16, bank 0)       | 49 |

|   | 8.9  | RAM_CFG_TBL_CRC (Address 0x17, bank 0)        | 50 |

|   | 8.10 | TBL_CRC_CHK_TSLD (Address 0x18, bank 0)       | 50 |

|   | 8.11 | DIAG_REG_1 (Address 0x19, bank 0)             | 51 |

|   | 8.12 | DIAG_REG_2 (Address 0x1A, bank 0)             | 52 |

|   | 8.13 | DIAG_REG_3 (Address 0x1B, bank 0)             | 53 |

|   | 8.14 | MEMT_CFG1_TBLX (Address 0x11, bank 1-16)      | 54 |

|   | 8.15 | MEMT_CFG2_TBLX (Address 0x12, bank 1-16)      | 55 |

|   | 8.16 | MEMT_CFG3_TBLX (Address 0x13, bank 1-16)      | 57 |

|   | 8.17 | MEMT_CFG4_TBLX (Address 0x14, bank 1-16)      | 58 |

|   | 8.18 | MEMT_CFG5_TBLX (Address 0x15, bank 1-16)      | 58 |

|   | 8.19 | MEMT_CFG6_TBLX (Address 0x16, bank 1-16)      | 59 |

|   | 8.20 | MEMT_CFG7_TBLX (Address 0x17, bank 1-16)      | 60 |

|   | 8.21 | OTP (Address 0x17-0x1F, bank 17)              | 60 |

| 9  | Application information     | 61 |

|----|-----------------------------|----|

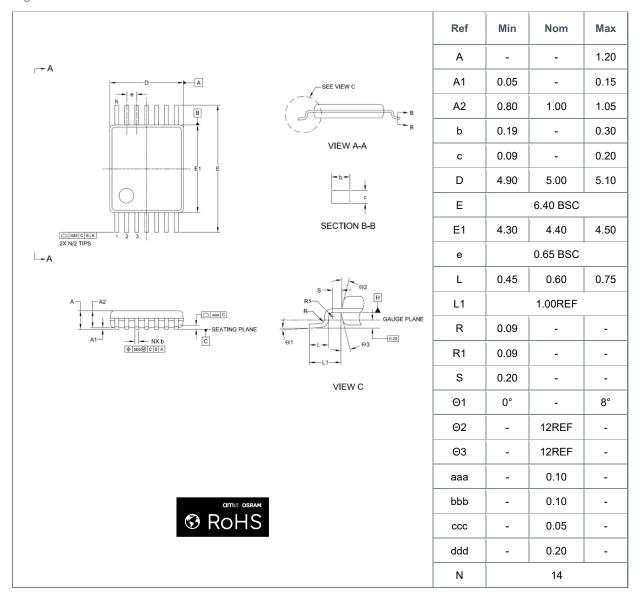

| 10 | Package drawings & markings | 62 |

| 11 | Revision information        | 64 |

| 12 | Legal information           | 65 |

## **AS8580 Capacitive sensor**

### 1 General description

AS8580 is a capacitive sensor detecting the change of capacitance in different applications. The capacitive sensor measures the relative change of capacitance. This can be used for capacitive touch applications, proximity or human presence detection, fluid level and quality measurements as well as many other applications.

AS8580 captures the sinusoidal current response caused by a forced sinusoidal voltage. Based on that, the change of capacitance in various applications can be detected. Besides capacitive changes, the resistive component in various applications can be detected as well.

This can be useful e.g. to determine/compensate (environmental) disturbances such as moisture, which changes a parallel resistive component along with a change in capacitance.

This high precision performance sensor also supports a multitude of diagnostic features that meet standard ASIL B functional safety requirements.

The capacitive sensing IC is specifically designed to work under high electromagnetic disturbances (EMC) due to adjustable frequencies.

AS8580 has a SPI Interface for reading measurement values and configuration.

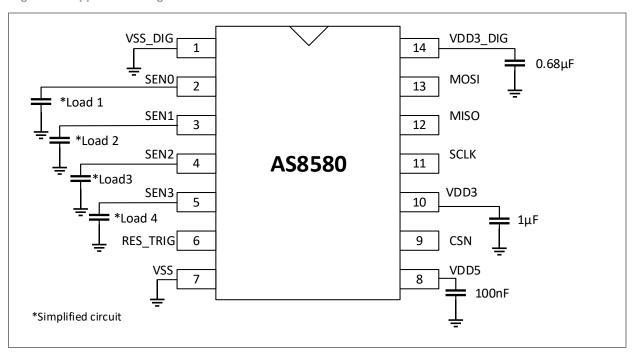

It is available in TSSOP-14 package and operates with 5V.

#### 1.1 Key benefits & features

The benefits and features of AS8580, Capacitive sensor are listed below:

Table 1: Added value of using AS8580

| Benefits                                                        | Features                                                                              |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Very accurate capacitive measurement with excellent sensitivity | Separation of resistive and capacitive components of measured impedance               |

| Touchless and wear free technology                              | Four independent measurement lines.                                                   |

| Outstanding quality and high durability at lower system costs   | Long term delivery and quality due to ams OSRAM own production site in central Europe |

| Enabler for safety critical applications                        | Functional safety ASIL B according ISO26262                                           |

| Suitable for automotive environment                             | AEC-Q100 Grade 1 qualified                                                            |

#### 1.2 Application example

- Autonomous driving applications, e.g.: Hands on steering wheel detection

- Automotive door handle / trunk opening applications

- · Human presence detection for automotive and non-automotive applications

- Sensing of fluid level and quality in vehicles as well as industrial applications

#### 1.3 Block diagram

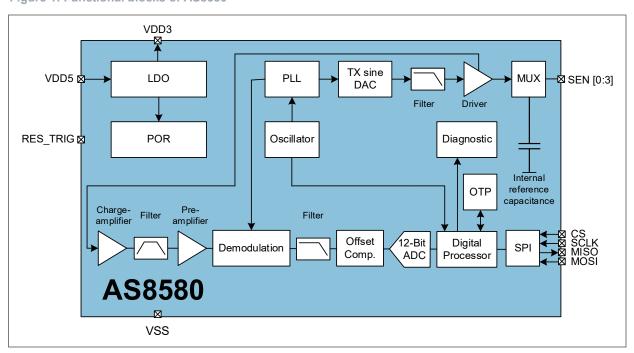

The functional blocks of this device are shown below in Figure 1:

Figure 1: Functional blocks of AS8580

## 2 Ordering information

| Product type | Ordering code | Package | Marking | Delivery form | Delivery quantity |

|--------------|---------------|---------|---------|---------------|-------------------|

| AS8580-ATST  | Q65113A8911   | TSSOP14 | AS8580  | Tape & reel   | 4,500 pcs/reel    |

| AS8580-ATSM  | Q65115A1258   | TSSOP14 | AS8580  | Tape & reel   | 500 pcs/reel      |

## 3 Package

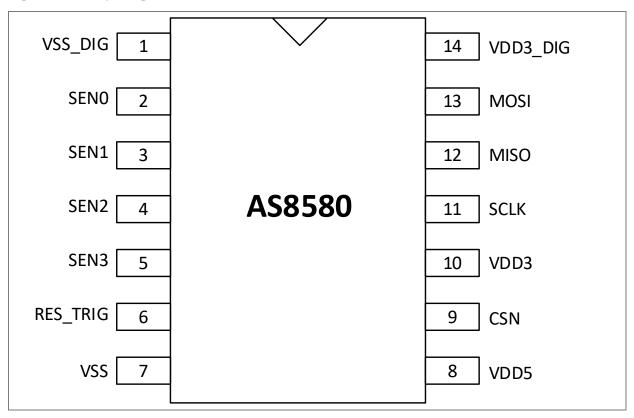

Figure 2: Plastic package TSSOP14

### 3.1 Pin description

Table 2: Pin description of AS8580

| Pin number | Pin name | Pin description                           | Pin type <sup>(1)</sup> | Notes              |

|------------|----------|-------------------------------------------|-------------------------|--------------------|

| 1          | VSS_DIG  | Digital ground                            | S                       |                    |

| 2          | SEN0     | Driver output                             | AIO                     |                    |

| 3          | SEN1     | Driver output                             | AIO                     |                    |

| 4          | SEN2     | Driver output                             | AIO                     |                    |

| 5          | SEN3     | Driver output                             | AIO                     |                    |

| 6          | RES_TRIG | Reset/trigger & Trigger mode indicator    | DIO_PUOD                |                    |

| 7          | VSS      | Analog ground                             | S                       |                    |

| 8          | VDD5     | 5V power supply                           | S                       |                    |

| 9          | CSN      | SPI chip select                           | DI_SPU                  | Selectable pull-up |

| 10         | VDD3     | 3.3V regulated output                     | S                       |                    |

| 11         | SCLK     | SPI clock                                 | DI_S                    |                    |

| 12         | MISO     | SPI data out                              | DO_T                    |                    |

| 13         | MOSI     | SPI data in                               | DI_S                    |                    |

| 14         | VDD3_DIG | 3.3V regulated output, for digital blocks | S                       |                    |

| (1) | S   | Supply     |  |  |  |

|-----|-----|------------|--|--|--|

|     | AIO | Analog I/O |  |  |  |

DI\_S Digital input with Schmitt-trigger

DI\_SPU Digital input with Schmitt-trigger and pull-up

DO\_T Digital output / tri-state

DIO\_PUOD Digital input-output with pull-up / open drain

## 4 Absolute maximum ratings (non-operating)

Stresses beyond those listed under "Absolute maximum ratings (non-operating)" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Electrical Characteristics.

"Operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3: Absolute maximum ratings of AS8580

| Parameter                         | Symbol        | Min  | Max      | Unit  | Note                                       |

|-----------------------------------|---------------|------|----------|-------|--------------------------------------------|

| DC supply voltage                 | VDD5          | -0.3 | 7        | V     | Referenced to VSS                          |

| Internal DC supply voltage        | VDD3 VDD3_DIG | -0.3 | 5        | V     | Referenced to VSS<br>Referenced to VSS_DIG |

| Difference between VSS-pins       | ΔVSS          | -0.3 | 0.3      | V     | VSS-VSS_DIG                                |

| Analog IO-pin voltage             | VAIO          | -0.3 | VDD5+0.3 | V     | Referenced to VSS                          |

| Digital IO-pin voltage            | VDIO          | -0.3 | VDD5+0.3 | V     | Referenced to VSS_DIG                      |

| Input current (latch-up immunity) | I_SCR         | -100 | 100      | mA    | AEC-Q100-004                               |

| Electrostatic discharge           | ECD 114       | ±4   |          | kV    | AEC-Q100-002                               |

| human body model                  | ESD_H1        | 14   |          | ΚV    | SENX pins                                  |

| Electrostatic discharge           | ESD H3        | ±2   |          | 1.3.7 | AEC-Q100-002                               |

| human body model                  | ESD_H2        | IZ   |          | kV    | All other pins                             |

| Storage temperature               | TEMP_STRG     | -55  | 150      | °C    |                                            |

| Package body temperature          | TEMP_BODY     |      | 260      | °C    | IPC/JEDEC J-STD-020 <sup>(1)(2)</sup>      |

| Moisture sensitivity level        | MSL           |      | 3        |       | ICP/JEDEC J-STD-033                        |

<sup>(1)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020C "Moisture/reflow sensitivity classification for non-hermetic solid state surface mount devices".

<sup>(2)</sup> The lead finish for Pb-free leaded packages is "Matte Tin" (100% Sn).

### 5 Electrical characteristics

#### 5.1 Operating conditions

Operating range defines the limits for functional operation and parametric characteristics of the device. The functionality of the sensor outside the operating range described in this section is not guaranteed. If not differently reported all values in the table below refer to the complete temperature range.

**Table 4: Operating conditions**

| Parameter                                               | Symbol         | Min | Тур | Max | Unit | Note                                                                                                  |

|---------------------------------------------------------|----------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------|

| DC supply voltage                                       | VDD5           | 4.5 | 5   | 5.5 | V    | Ramp-up time from 0 to 2.5V<br>must be less than 20msec<br>Referenced to VSS                          |

| Digital DC supply voltage                               | VDD3_DIG       | 3   | 3.3 | 3.6 | V    | Referenced to VSS_DIG, internally generated                                                           |

| Analog DC supply voltage                                | VDD3           | 3   | 3.3 | 3.6 | V    | Referenced to VSS, internally generated                                                               |

| Negative supply voltage,<br>analog, digital             | VSS<br>VSS_DIG |     | 0   |     | V    | VSS-VSS_DIG is the reference for all other nodes                                                      |

| Difference between VSS-pins                             | ΔVSS           |     | 0   |     | V    | VSS and VSS_DIG must be connected together on PCB in all applications                                 |

| Supply current during measurement                       | IDD_MEAS       |     | 16  |     | mA   | With external electrode enabled.                                                                      |

| Average supply current in polling mode (see conditions) | IDD_POLL       |     | 105 |     | μА   | 60µs settling, 36ms period, 2 electrodes enabled, accumulation 2 values, room temperature, 5V supply. |

| Power save supply current                               | IDD_PS         |     |     | 20  | μΑ   | In polling mode, after<br>measurement completion.<br>Room temperature                                 |

|                                                         | -              |     |     | 50  | μA   | Full temperature range                                                                                |

| Supply current in wait mode                             | IDD_WAIT       |     | 1   |     | mA   |                                                                                                       |

| Ambient temperature                                     | TEMP_AMB       | -40 |     | 125 | °C   |                                                                                                       |

### 5.2 DC/AC characteristics for inputs and outputs

#### 5.2.1 Analog in- and outputs

Table 5: CMOS in-/output, pin type: AIO (pins: SEN0-SEN3)

| Parameter             | Symbol | Min | Max | Unit | Note                          |

|-----------------------|--------|-----|-----|------|-------------------------------|

| Input leakage current | I_LEAK |     | 10  | μΑ   |                               |

| Input capacitance     | C_IN   |     | 10  | pF   | Info parameter <sup>(1)</sup> |

<sup>(1)</sup> Info Parameters are not pass/fail parameters in production where limits are calculated from simulation and characterization.

#### 5.2.2 Digital inputs

Table 6: CMOS digital input with Schmitt-trigger, pin type: DI\_S (pins: MOSI, SCLK, CSN)

| Parameter                   | Symbol | Min        | Max        | Unit | Note        |

|-----------------------------|--------|------------|------------|------|-------------|

| High level input voltage    | V_IH   | 0.7 * VDD5 |            | V    |             |

| Low level input voltage     | V_IL   |            | 0.3 * VDD5 | V    |             |

| Negative-going threshold    | VT_N   | 1.9        | 2.4        | V    | VDD5 = 5.5V |

| Positive-going threshold    | VT_P   | 3          | 3.5        | V    | VDD5 = 5.5V |

| Input leakage current       | I_LEAK | -1         | 1          | μA   | V_IH = 5.5V |

| Pull-up current (pins: CSN) | I_PU   | -250       | -50        | μΑ   | V_IL = 0.0V |

#### 5.2.3 Digital outputs

Table 7: CMOS digital output tri-state, pin type: DO\_T (pins: MISO)

| Parameter                 | Symbol | Min        | Max       | Unit | Note        |

|---------------------------|--------|------------|-----------|------|-------------|

| High level output voltage | V_OH   | VDD5 - 0.5 |           | V    |             |

| Low level output voltage  | V_OL   |            | VSS + 0.4 | V    |             |

| Output drive strength     | I_OH   |            | 1         | mA   | VDD5 = 4.5V |

| Output drive strength     | I_OL   |            | 1         | mA   | VDD5 = 4.5V |

| Tri-state leakage current | I_OZ   | -10        | 10        | μΑ   | To VSS      |

Table 8: CMOS digital input-output open drain with pull-up, pin type: DIO\_PUOD (pins: RES\_TRIG)

| Parameter                 | Symbol | Min        | Max        | Unit | Note        |

|---------------------------|--------|------------|------------|------|-------------|

| High level input voltage  | V_IH   | 0.7 * VDD5 |            | V    |             |

| Low level input voltage   | V_IL   |            | 0.3 * VDD5 | V    |             |

| Low level output voltage  | V_OL   |            | VSS + 0.4  | V    |             |

| Output drive strength     | I_OL   |            | 4          | mA   | VDD5 = 4.5V |

| Tri-state leakage current | I_OZ   | -10        | 10         | μΑ   | To VSS      |

| Pull-up resistance        | R_PU   | 6          | 15         | kΩ   |             |

#### 5.3 Internal ESD protection concept

#### **VSS** supply domain

VSS and VSS\_DIG must be connected together in all applications.

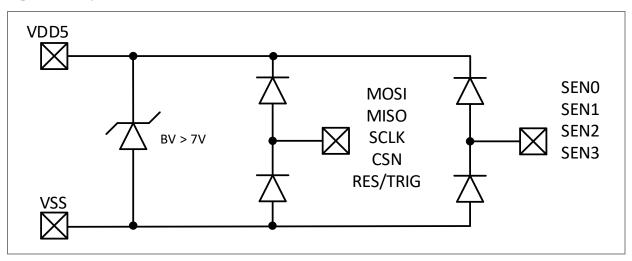

#### VDD5 supply domain

Figure 3: ESD protection circuit on VDD5 domain

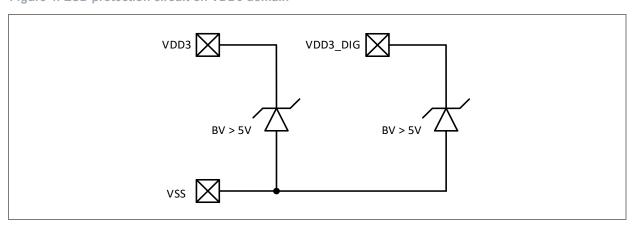

#### 3.3V supply domains

Figure 4: ESD protection circuit on VDD3 domain

Table 9: ESD protection on VDD5 domain

| Parameter                               | Min | Max | Unit | Note                                                     |

|-----------------------------------------|-----|-----|------|----------------------------------------------------------|

| Positive ESD clamp voltage              | 7   |     | V    | Info parameter <sup>(1)</sup>                            |

| Positive ESD protection leakage current |     | 1   | μΑ   | 0 <v<7 t="25°C&lt;br">Info parameter<sup>(1)</sup></v<7> |

<sup>(1)</sup> Info Parameters are not pass/fail parameters in production where limits are calculated from simulation and characterization

Table 10: ESD protection on VDD3 and VDD3\_DIG domains

| Parameter                               | Min | Max | Unit | Note                                                     |

|-----------------------------------------|-----|-----|------|----------------------------------------------------------|

| Positive ESD clamp voltage              | 5   |     | V    | Info parameter <sup>(1)</sup>                            |

| Positive ESD protection leakage current |     | 1   | μΑ   | 0 <v<5 t="25°C&lt;br">Info parameter<sup>(1)</sup></v<5> |

<sup>(1)</sup> Info Parameters are not pass/fail parameters in production where limits are calculated from simulation and characterization

## 6 Functional description

The purpose of this sensor is to measure a sensor capacitance at four pins, SEN0 to SEN3.

The measurement is realized with a transceiver architecture operating between 5MHz and 20MHz. In short, the transmitter forces a sine wave voltage across the load to measure; and the receiver detects the current response of the load. The current response is converted to a voltage and then demodulated; this is then filtered and converted in 12-bit digital words; it is possible to accumulate the digital words for noise reduction. The architecture allows the detection of not only capacitive changes, but also of changes due to environmental factors such as moisture, which adds a parallel resistive component along with a change in capacitance.

The response can be measured on any of the 4 SEN pins connected to the sensor driver through an analog multiplexer. The carrier frequency of 5-20MHz is generated by a PLL frequency synthesizer; an optional spread spectrum function varies the frequency of the carrier signal in order to reduce the emission level by spreading the RF energy over a broader band.

#### 6.1 Operation modes overview

The device can operate in different modes: Initialization, single measurement, continuous measurement, polling measurement, diagnostic, and low power modes.

Once the voltage at VDD3\_DIG crosses the POR release threshold the digital control logic starts functioning; the NOT\_INIT bit in the diagnostic register is set; the OTP contents are loaded and the VDD3 LDO is turned on. Once the voltage at VDD3 crosses the POR release threshold the device completes the startup sequence and starts generating a trigger pulse on RES\_TRIG.

The device remains in this state until it receives a CLEAR\_NOT\_INIT command; no other command will be accepted in this phase.

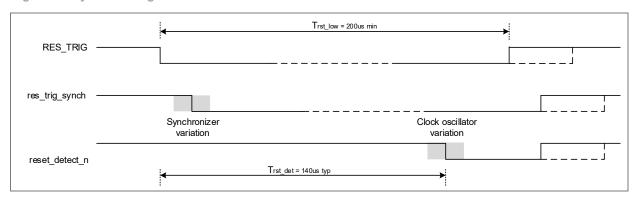

At any time, a low pulse on RES\_TRIG of at least TRST\_LOW will reset the device.

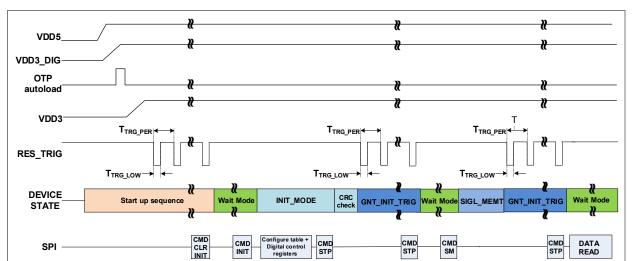

The power-up sequence waveform is given below.

Figure 5: Power-up sequence

#### The state diagram of the device is given below:

Figure 6: State diagram

#### 6.2 Generate trigger mode

The device generates a trigger pulse on RES\_TRIG to notify that it is ready to accept new commands.

It can enter wait mode after receiving a STOP command.

#### 6.3 Wait mode

The device enters wait mode at startup after receiving a CLEAR NOT INIT command.

It can also enter this mode from all other modes after receiving a STOP command.

From this mode the device can enter into any mode through SPI command.

#### 6.4 Initialization mode

This mode can be entered only from wait mode following an INIT\_MODE command.

The device can be configured via SPI; writing to configuration tables in any other mode is not possible; any attempt to do so will result in the INVALID SPI WRITE flag being set.

Once the MCU completes configuring tables and control registers, exit from this mode is possible by sending a STOP command. On STOP command if TBL\_CRC\_CHK\_TSLD is non-zero then the configuration table CRC check will be executed. On completion of CRC check the device enters into generate trigger mode and then enters wait mode by STOP command.

'0' in TBL\_CRC\_CHK\_TSLD will result into device entering generate trigger mode without configuration table CRC check.

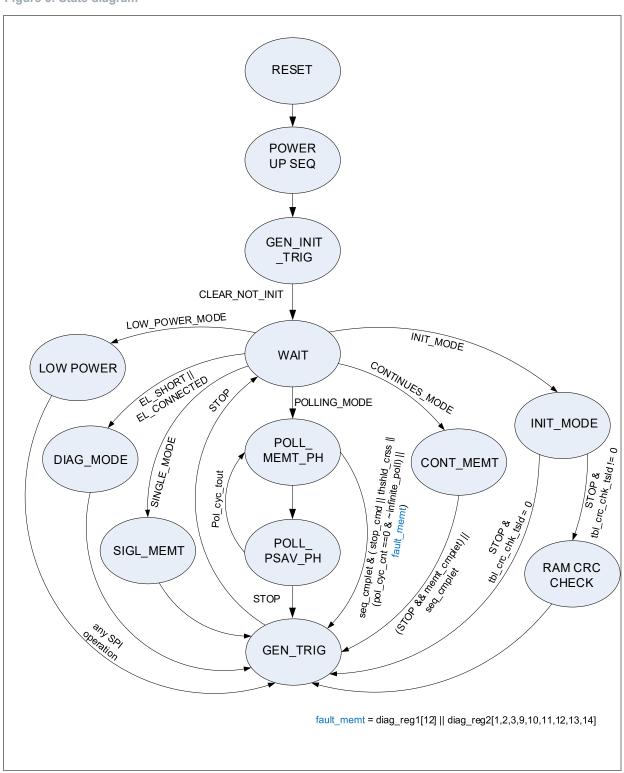

#### 6.5 Single measurement mode

This mode can be entered only from wait mode following a SINGLE MODE command.

The device should be properly configured before entering this mode.

Once into this mode, old measurement data is cleared from memory; a new measurement is executed with the configuration table settings pointed by MEMT\_STRT\_PTR; MEMT\_SEQ content is ignored.

Each conversion will take between 45 and 300 µs, depending on the LPF settling time defined in SETTLING DCLPF.

Measurement data will be stored at a location corresponding to the active configuration table.

Once the measurement is complete the device enters the generate trigger mode; it will go back to wait mode after receiving a STOP command.

The single measurement operation waveform and flowchart are given below.

Figure 7: Single measurement operation waveform

Start single measurement command at defined table line

Clear old data from memory

Load the settings of Configuration table selected by MEMT\_STRT\_PTR

I channel measure & store data in respective address

Generate Trigger

STOP Commad?

No

Yes

Wait state (data read)

Figure 8: Single measurement operation flowchart

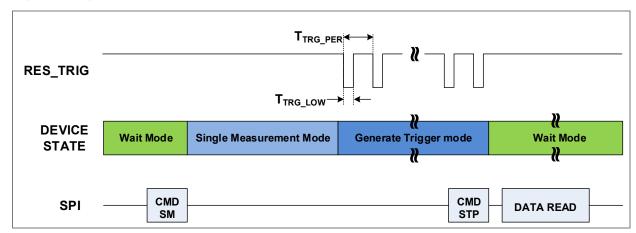

#### 6.6 Continuous measurement mode

This mode can be entered only from wait mode following a CONTINUOUS MODE command.

The device should be properly configured before entering this mode.

Once into this mode, old measurement data is cleared from memory; a sequence of measurements is executed using settings written in the configuration tables enabled in MEMT\_SEQ, and starting with the table pointed by MEMT\_STRT\_PTR; more information can be found in chapter 6.11.

Measurement data will be stored at a location corresponding to the active configuration table.

Once the measurement is complete the device enters into the generate trigger mode; it will go back to wait mode after receiving a STOP command.

The continuous measurement operation waveform and flowchart are given below.

Figure 9: Continuous measurement operation waveform

Start Continuous measurement command at defined table line Clear old data from memory Set starting point of sequence pointed by MEMT\_STRT\_PTR Load the settings of Configuration table selected in MEMT\_SEQ measure & store data in respective address STOP command? No Move pointer to next set bit in MEMT\_SEQ Sequence complete Yes Generate Trigger STOP Commad ? ¥Yes Wait state (data read)

Figure 10: Continuous measurement operation flowchart

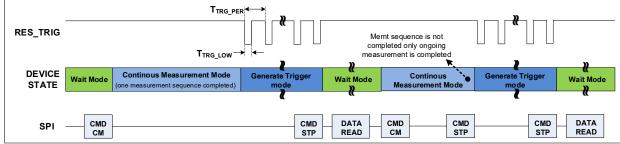

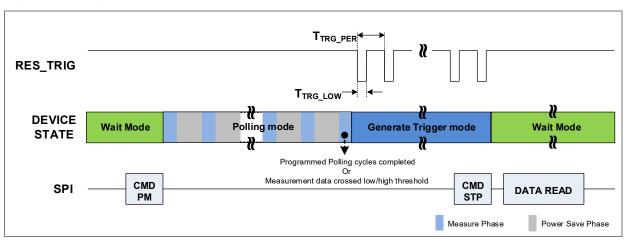

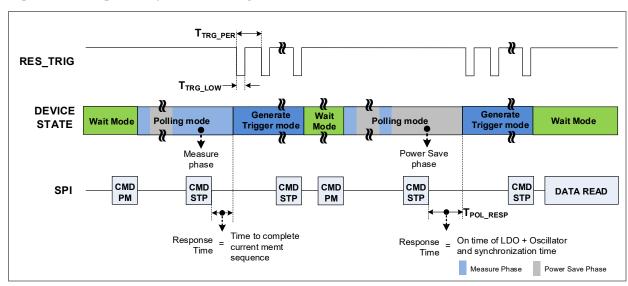

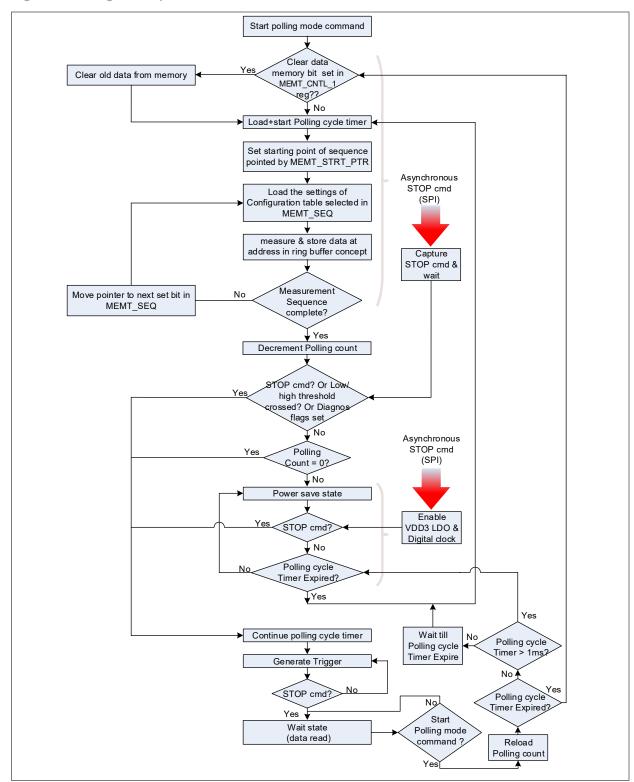

#### 6.7 Polling measurement mode

This mode can be entered only from wait mode following a POLLING\_MODE command.

The device should be properly configured before entering this mode.

Once into this mode, old measurement data is cleared from memory if the clear memory bit is high.

Measurements are executed in sequence as in continuous mode, as described in chapter 6.11.

The device repeats the measurement sequence for a number of times specified in POLL\_CYC\_CNT; the limit can be disabled by setting INFINITE\_POLLING.

The interval between the starting point of two measurement sequences can be selected from 12 to 128 ms acting on POLL\_TIME.

Measurement data is stored according to a FIFO buffer concept: The latest value is always saved at address 0x00, the second-last at address 0x01, etc.

After every measurement the data is compared with THRESHOLD\_LOW and THRESHOLD\_HIGH of the corresponding configuration table. If the measured data crosses any of these lower or higher thresholds then the respective flag will be set in DIAG\_REG\_1.

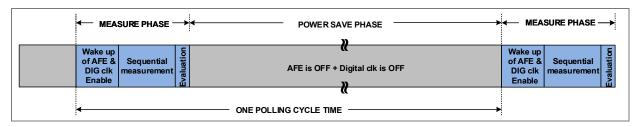

Between the completion of a measurement sequence and the start of the next one the device enters a power save state; all AFE blocks and the oscillator block are turned off; the VDD3 regulator is off; a low frequency oscillator and the polling cycle timer will be working in this phase.

Any SPI transaction during the power save state will enable the oscillator, which will keep working until the next measurement phase; in this case there will be an additional power consumption due to the oscillator running.

An SPI transaction is recognized after 5 pulses of SCLK past the falling edge of CSN.

After the total number of polling cycles are completed or if any threshold cross flags are set or any diagnostic events are detected, then the device enters into generate trigger mode; it will go back to wait mode after receiving a STOP command. It is also possible to terminate the polling mode by sending a STOP command; the device will complete the current measurement sequence then enter into generate trigger mode. Any other command will be ignored.

If TBL\_CRC\_CHK\_TSLD is non-zero then the configuration table CRC check will be executed every TBL\_CRC\_CHK\_TSLD measurement sequences; a CRC check lasts for 116 clock cycles (29µs typ.).

Following are some operation waveforms and a flowchart of polling mode:

Figure 11: Polling cycle waveform

Figure 12: Polling mode operation

Figure 13: Polling mode operation with asynchronous STOP command

Figure 14: Polling mode operation flowchart

#### 6.8 Low power mode

This mode can be entered only from wait mode following a LOW\_PWR\_MODE command.

Any SPI operation will cause the device to enter into generate trigger mode.

#### 6.9 Diagnostic modes

Diagnostics is implemented to ensure all blocks are operating within their operating range (not only functional) to allow robust determination when the system may not be able to properly detect the capacitance change. This applies not only to the functionality of the sensor but also to the interface.

When the  $\mu$ C is not performing the EL\_CONNECTED diagnostic the connection between the electrode and the  $\mu$ C itself has to be tri-stated.

#### Information:

CUSTOMER shall take care that any non-ideal effect (PSRR, Impedance, etc.) due to the connection of the  $\mu$ C to the electrodes will not affect the measurement.

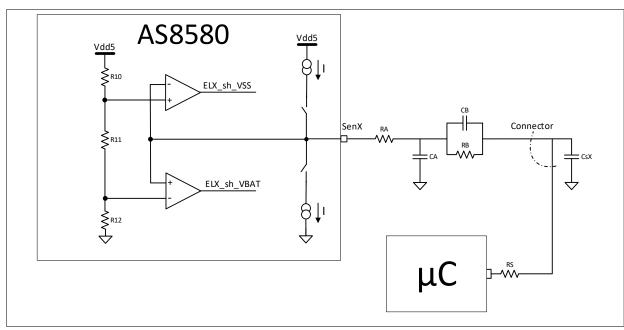

The simplified schematic diagram in diagnostic mode is given below.

Figure 15: Diagnostic concept

Two dedicated diagnostic modes are in place to verify that the electrodes are not shorted to VSS nor to VBAT and that the electrodes are connected to the device.

In EL SHORT mode the device is able to detect a short to VBAT or GND.

On every selected sensor pin two current mirrors force sequentially a positive and negative current and a couple of comparators check that the voltage stays close to VDD5 and VSS, respectively.

The relevant bits of DIAG\_REG\_1 are then updated; the completion of this procedure is communicated to the host through pulses on RES\_TRIG until a STOP command is received.

In EL CONNECTED mode the device is able to detect an open connection.

To perform this diagnostic function the µC has to first force the electrodes to VSS.

After a settling time from the mode change command the sensor forces a positive current on each selected electrode and a comparator checks that the voltage stays close to VSS.

The relevant bits of DIAG\_REG1 are then updated; the completion of this procedure is communicated to the host through pulses on the RES\_TRIG pin until a STOP command is received from SPI.

Sensor pins can be individually enabled by writing on ELEC\_DIAG\_SEL.

**Table 11: Diagnostic function**

| Parameter                       | Symbol         | Min | Тур       | Max | Unit | Note                             |

|---------------------------------|----------------|-----|-----------|-----|------|----------------------------------|

| Short to VSS threshold          | TH_DIAG_VSS    |     | 0.9*VDD5  |     | V    | Info<br>parameter <sup>(1)</sup> |

| Short to VBAT threshold         | TH_DIAG_VBAT   |     | 0.15*VDD5 |     | V    | Info<br>parameter <sup>(1)</sup> |

| Short to VBAT bias current      | I_DIAG_SH_VBAT | 250 | 360       | 500 | μΑ   | Info<br>parameter <sup>(1)</sup> |

| Short to VSS bias current       | I_DIAG_SH_VSS  | 80  | 120       | 160 | μΑ   | Info<br>parameter <sup>(1)</sup> |

| Bias current<br>EL_CONNECTED    | I_DIAG_CONN    | 14  | 20        | 30  | μΑ   | Info<br>parameter <sup>(1)</sup> |

| Evaluation time EL_SHORT        | T_DIAG_SH      |     | 120       |     | μs   | One electrode                    |

| Evaluation time<br>EL_CONNECTED | T_DIAG_CONN    |     | 60        |     | μs   | One electrode                    |

<sup>(1)</sup> Info Parameters are not pass/fail parameters in production where limits are calculated from simulation and characterization.

#### 6.10 Diagnostic features

The device performs a number of diagnostic checks at various phases; the results are available as diagnostic flags. Some checks also cause the device to exit polling mode after the measurement sequence is completed and to enter the generate trigger mode. A list is given below.

Table 12: List of diagnostic checks

| Diagnostic feature                                | Enabled                                | Effect                    | Note |

|---------------------------------------------------|----------------------------------------|---------------------------|------|

| EL_SHORT                                          | By command                             | Diag. flag                |      |

| EL_CONNECTED                                      | By command                             | Diag. flag                |      |

| Undervoltage VDD5                                 | During measurement                     | Diag. flag + Stop polling |      |

| Undervoltage VDD3                                 | During measurement                     | Diag. flag + Stop polling |      |

| Overvoltage VDD3                                  | During measurement                     | Diag. flag + Stop polling |      |

| Overvoltage VDD3 DIG                              | During measurement                     | Diag. flag + Stop polling |      |

| Overcurrent VDD3                                  | During measurement                     | Diag. flag + Stop polling |      |

| Overcurrent VDD3 DIG                              | During measurement                     | Diag. flag + Stop polling |      |

| Thermal protection                                | During measurement                     | Diag. flag + Stop polling |      |

| PLL lock fail                                     | During measurement                     | Diag. flag + Stop polling |      |

| Electrode driver overcurrent                      | During measurement                     | Diag. flag + Stop polling |      |

| Measurement data crossed upper or lower threshold | During measurement                     | Diag. flag + Stop polling |      |

| CRC on RAM fail                                   | During measurement and after CRC write | Diag. flag + Stop polling |      |

| NOT_INIT                                          | During power-up                        | Diag. flag                |      |

| RAM BIST TEST fail                                | During power-up                        | Diag. flag                |      |

| OTP_FAIL                                          | During power-up                        | Diag. flag                |      |

| SPI_PARITY                                        | After SPI frame                        | Diag. flag                |      |

| SHORT/LONG SPI                                    | After SPI frame                        | Diag. flag                |      |

| NO BANK ACCESS                                    | After SPI frame                        | Diag. flag                |      |

| INVALID_SPI_WRITE                                 | After SPI frame                        | Diag. flag                |      |

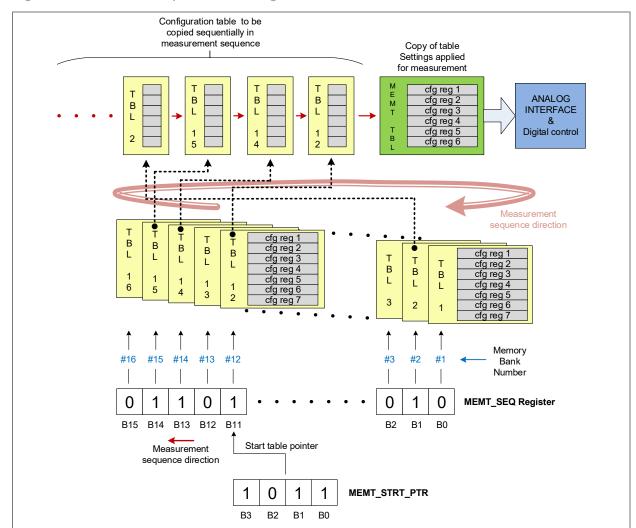

#### 6.11 Measurement sequence with configuration tables

The concept of measurement sequence with different configuration settings applied is shown in the following diagram:

Figure 16: Measurement sequence with configuration tables

A measurement sequence begins with the configuration table pointed by MEMT\_STRT\_PTR, then the table pointer is increased. If a bit in the MEMT\_SEQ is 1 then the corresponding configuration table will be part of the sequential measurement; if it is 0 the table will not be used. The settings in the selected tables will be used when their turn arrives. A sequence is completed once all 16 tables are checked and processed accordingly.

#### **6.12** Chip ID

All devices are provided with a unique ID code stored at addresses 0x1C:0x1E in the OTP memory.

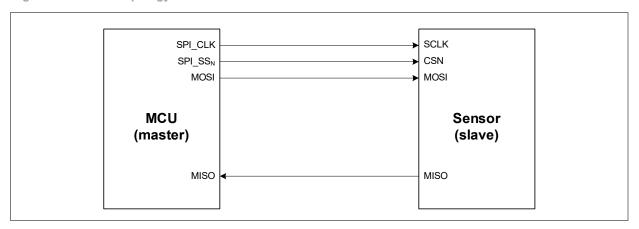

#### 6.13 SPI interface

The sensor communicates through a serial peripheral interface (SPI), consisting of Serial Clock (SCLK), Data Out (MISO), Data In (MOSI), and Chip Select (CSN) pins. The sensor acts as SPI slave.

Figure 17: SPI bus topology

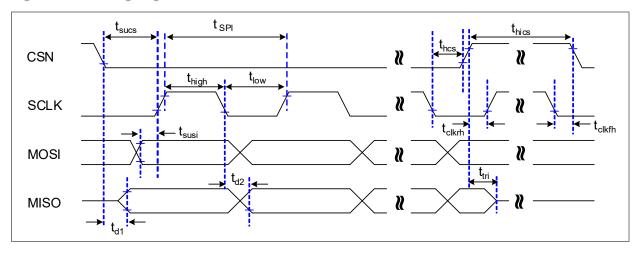

The SPI transaction begins when CSN is asserted (driven low). On every positive edge of SCLK, master and slave sample data on MISO and MOSI, respectively. On every negative edge of SCLK, master and slave send data on MOSI and MISO, respectively. The SPI transaction ends when CSN goes high. A complete SPI transaction contains 24 SCLK cycles. Shorter or longer transactions will result in errors being reported in the diagnostic register. A time diagram of an SPI transaction is shown below.

SCLK

MOSI

RW A4 A3 A2 A1 A0 0 PR D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X

Commad N

Data of Commad N-1

Data of Commad N-1

Data of Commad N-1

- Sampling Edge

- Don't care data

Figure 18: SPI transaction detailed diagram

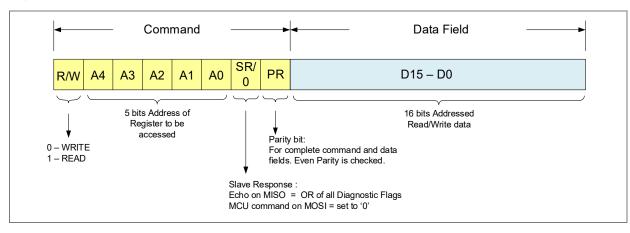

An SPI frame is composed by an 8-bit command, followed by a 16-bit data field. The SPI frame format is shown in following diagram.

Figure 19: SPI frame format

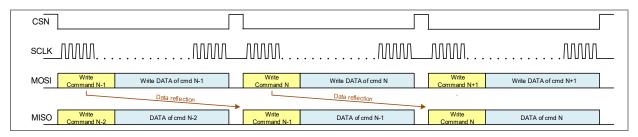

Two types of SPI transfers are possible, write and read. The device always transmits data relative to the previous transaction; it echoes the previous command in the command field and sends data of the previously addressed register in the data field. Below are examples of write and read transactions.

Figure 20: SPI write transaction

Figure 21: SPI read transaction

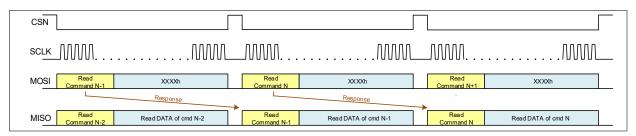

In the system it is required to validate data written through SPI. This can be done by a dedicated read transaction or by reading the register just written during the next write transaction. Both methods are illustrated in the following diagram.

Figure 22: SPI write operation data check methods

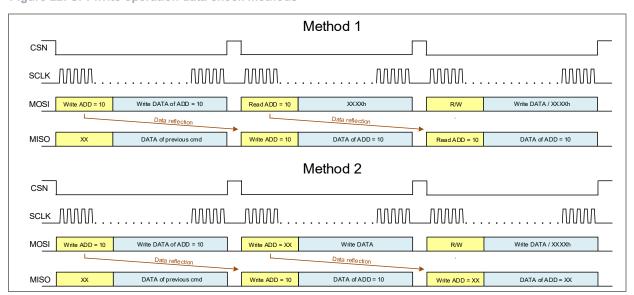

### 6.14 SPI timing characteristics

Figure 23: SPI timing diagram

**Table 13: SPI timing characteristics**

| Parameter                         | Symbol             | Min  | Тур                 | Max | Unit | Note                   |

|-----------------------------------|--------------------|------|---------------------|-----|------|------------------------|

| SCLK period                       | t <sub>SPI</sub>   | 125  |                     |     | ns   | Max frequency is 8 MHz |

| SCLK high time                    | $t_{high}$         | 57.5 | 62.5                | -   | ns   |                        |

| SCLK low time                     | $t_{\text{low}}$   | 57.5 | 62.5                | -   | ns   |                        |

| CSN setup time                    | t <sub>sucs</sub>  | 57.5 | 62.5                | -   | ns   |                        |

| Delay time 1                      | $t_{d1}$           | -    | -                   | 40  | ns   |                        |

| MOSI setup time                   | t <sub>susi</sub>  | 15   | -                   | -   | ns   |                        |

| Delay time 2                      | $t_{d2}$           | -    | -                   | 40  | ns   |                        |

| CSN hold time                     | t <sub>hcs</sub>   | 57.5 | T <sub>SPI</sub> /2 | -   | ns   |                        |

| Tri-state delay time              | t <sub>tri</sub>   | -    | -                   | 30  | ns   |                        |

| CSN high time                     | t <sub>hics</sub>  | 1250 | -                   | -   | ns   |                        |

| SCLK hold time after CSN rising   | t <sub>clkrh</sub> | 10   | -                   | -   | ns   |                        |

| SCLK hold time before CSN falling | t <sub>clkfh</sub> | 10   | -                   | -   | ns   |                        |

## 7 Detailed system and block specification

### 7.1 System timing

Figure 24: System timing

**Table 14: System timing**

| Parameter                                                                  | Symbol    | Min | Тур | Max | Unit | Note                                           |

|----------------------------------------------------------------------------|-----------|-----|-----|-----|------|------------------------------------------------|

| Low time of trigger pulse                                                  | TTRG_LOW  | 14  | 16  | 18  | μs   |                                                |

| Trigger pulse period                                                       | TTRG_PER  | 4   | 7   | 10  | ms   |                                                |

| Minimum low time on RES_TRIG to reset the device                           | TRST_LOW  | 200 |     |     | μs   |                                                |

| Reset detection time                                                       | TRST_DET  | 105 | 140 | 175 | μs   |                                                |

| Response time for STOP/SPI command during power save phase in polling mode | TPOL_RESP |     |     | 100 | μs   | Wait time before sending the next SPI command. |

| Polling time accuracy                                                      | TPOL_ACC  | -15 |     | 15  | %    | Polling time is selected via register          |

#### 7.2 System parameters

**Table 15: System parameters**

| Parameter                             | Symbol     | Min | Тур | Max | Unit                      | Note                                                                                                                                                                       |

|---------------------------------------|------------|-----|-----|-----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver carrier frequency         | AFE_FREQ   | 5   |     | 20  | MHz                       | Set via register <sup>(1)</sup>                                                                                                                                            |

|                                       |            |     |     |     |                           | Part-to-part variation                                                                                                                                                     |

| System sensitivity                    | AFE_SENS   |     | 1.9 |     | fF/LSB                    | PRE_GAIN 4;<br>PGA_GAIN -33.3; room<br>temperature; typical<br>supply; TX and RX filters<br>at 3 x AFE_FREQ; at the<br>AFE_FREQ factory<br>trimmed frequency<br>(7.43 MHz) |

| Wake up time                          | AFE_WAKEUP |     |     | 60  | μs                        | PLL prescaler ratio = 1<br>Info parameter <sup>(2)</sup>                                                                                                                   |

| Measurement time                      | AFE_TMEAS  |     | 210 |     | μs                        | Using 2 tables, 60µs LPF settling, PLL prescaler 1; add 15µs for each additional oversampling measurement.  Info parameter <sup>(2)</sup>                                  |

| System noise                          | AFE_N      |     | 4   |     | LSB<br>RMS <sup>(3)</sup> | Configuration as in AFE_SENS definition above; 2 accumulations; room temperature; typical process.                                                                         |

| System tolerance to temperature drift | AFE_TOL    |     | 5   | 40  | LSB/°C                    |                                                                                                                                                                            |

<sup>(1)</sup> Frequency over 15MHz is not pass/fail parameters in production where limits are calculated from simulation and characterization.

<sup>(2)</sup> Info Parameters are not pass/fail parameters in production where limits are calculated from simulation and characterization.

<sup>(3)</sup> Noise is calculated as the standard deviation of 100 measurements.

### 7.3 PLL

The PLL synthesizer generates a clock signal with frequency between 5 MHz and 20 MHz. The reference frequency is generated by a 4MHz oscillator conveniently divided by a prescaler to ensure an optimum PLL locking time. The oscillator frequency can be changed by ±160 kHz acting on RCO.

**Table 16: PLL parameters**

| Parameter                  | Symbol     | Min | Тур   | Max | Unit | Note                                                     |

|----------------------------|------------|-----|-------|-----|------|----------------------------------------------------------|

| Main clock frequency       | MCLK       | 3.8 | 4     | 4.2 | MHz  | Without spread spectrum.<br>Factory trimmed              |

| Frequency step             | OSC_STEP   |     | 80    |     | KHz  | Info parameter <sup>(1)</sup>                            |

| Oscillator switch-off time | OSC_OFF    |     | 2     |     | μs   | Info parameter <sup>(1)</sup>                            |

| Start-up time              | OSC_ON     |     | 2     |     | μs   | Info parameter <sup>(1)</sup>                            |

| PLL input frequency        | PLL_FIN    | 0.1 |       | 4.2 | MHz  | Reference frequency                                      |

| PLL output frequency       | PLL_FOUT   | 5   |       | 20  | MHz  |                                                          |

| VCO phase resolution       | PLL_PHRES  |     | 11.25 |     | deg  | Info parameter <sup>(1)</sup>                            |

| Settling time 00b          | PLL_TS0    |     | 5     |     | μs   | Prescaler ratio = 1                                      |

| Settling time 01b          | PLL_TS1    |     | 20    |     | μs   | Prescaler ratio = 7                                      |

| PLL bandwidth              | PLL_BW     |     | 100   |     | KHz  | Info parameter <sup>(1)</sup>                            |

| Spread spectrum deviation  | PLL_SS_DEV | 0   |       | 10  | %    | Selectable via register<br>Info parameter <sup>(1)</sup> |

<sup>(1)</sup> Info Parameters are not pass/fail parameters in production where limits are calculated from simulation and characterization.

#### 7.4 TX sine DAC / filter

The SINEDAC block generates a discrete sine wave with 16 samples per period; it uses 16 clock phases from the PLL VCO with 1/16 TCLK phase resolution. The SINEDAC is based on a resistive divider with variable R/R ratio.

These can be defined by using FREQ, PRESCALER, and TX\_LPF fields in the control registers.

The DAC output is filtered with a first order passive low-pass filter for noise reduction.

### 7.5 TX driver and current sensing

"Driver" module in block diagram. The transmitter topology is designed to optimize performance and power consumption across frequency. The output stage can drive a continuously changing capacitive load at 5 to 20 MHz providing a low impedance output. Overcurrent events are signaled through the OC\_DRIVER flag.

### 7.6 TX multiplexer

"MUX" module in block diagram. A multiplexer is implemented to connect the buffered sinewave signal to each sensor (SEN0 through SEN3) and/or an internal reference capacitance. The 30pF internal reference capacitance is sub ranged in 2pF steps with REFERENCE field in MEMT\_CNTL\_1 register.

SEN controls which sensors are connected during every measurement; it is possible to have more than one sensor connected at the same time.

Unused sensors can be shorted to ground by setting SEN TO GND.

### 7.7 Trans impedance amplifier

"Charge amplifier" in block diagram. The current-to-voltage conversion is performed by a transimpedance amplifier. The feedback impedance is predominantly capacitive in the operating frequency range; considering the sensor this creates a constant closed loop gain factor (C/C) over frequency.

The op-amp topology is designed to optimize performance in the entire frequency range.

### 7.8 Band pass filter / pre-amplifier

"Filter / Preamplifier" in Block Diagram. An AC coupled low-pass filter is implemented to ensure better EMC performance and minimize the effect of harmonics. The gain can be changed in order to optimize the signal to noise ratio. PRE\_GAIN bits can be used to control the gain, and RX LPF to define the cut-off frequency.

#### 7.9 Demodulation

The demodulation module multiplies the signal by ±1 using a passive switch. The absolute phase shift between the carrier signal (SINDAC block) and the clock can be programmed in steps of 11.25°.

### 7.10 Low pass filter

A third-order low-pass filter is needed to reject the  $2F_c$  and higher demodulator terms. A cutoff frequency of 40 KHz was chosen as a tradeoff between stop-band attenuation and settling time. The filter is a cascade of a second-order Sallen-Key stage and a first-order passive stage, providing a response close to a Bessel approximation.

### 7.11 Offset comp: Programmable gain amplifier

A programmable gain amplifier is used to further increase the level of the demodulated and filtered DC signal. The amplifier has a second input used to add or subtract an offset in order to shift the input range of the signal chain. The offset signal is generated by a 10-bit DAC.

Use register fields PGA GAIN ISET and PGA OV ISET to control this.

#### 7.12 ADC

A 12-bit SAR ADC is used to convert the analog signal into digital words.

The wait time from low-pass filter (see 7.10) power-up to A/D conversion can be adjusted from 20µs to 272µs by acting on SETTLING\_DCLPF.

Each conversion requires 14 clock cycles of 1µs (typical value).

### 7.13 Voltage regulators

Two independent voltage regulators are used to supply the digital and analog blocks with 3.3V; the voltage is factory trimmed. An external capacitor is required to ensure stability of each regulator.

### 7.14 Supply monitor

VDD5, VDD3, and VDD3DIG are constantly monitored in order to ensure that all internal blocks operate correctly.

Under-voltage of VDD3DIG generates a reset of the digital machine.

Other events are signaled through flags in the diagnostic register.

# 8 SW interface

**Table 17: Register overview**

| Addr. | Control & status | Table1         | Table2         |  | Table16         |  |  |  |  |

|-------|------------------|----------------|----------------|--|-----------------|--|--|--|--|

|       | Bank #00         | Bank #01       | Bank #02       |  | Bank #16        |  |  |  |  |

| (5b)  | (16b)            | (16b)          | (16b)          |  | (16b)           |  |  |  |  |

| 0x00  |                  | M              | IEMT_DATA_1    |  |                 |  |  |  |  |

| 0x01  |                  | M              | EMT_DATA_2     |  |                 |  |  |  |  |

| •     |                  |                | •              |  |                 |  |  |  |  |

| •     |                  |                | •              |  |                 |  |  |  |  |

| 0x0E  |                  | ME             | EMT_DATA_15    |  |                 |  |  |  |  |

| 0x0F  |                  | ME             | EMT_DATA_16    |  |                 |  |  |  |  |

| 0x10  |                  |                | BANK_SEL       |  |                 |  |  |  |  |

| 0x11  | MEMT_SEQ         | MEMT_CFG1_TBL1 | MEMT_CFG1_TBL2 |  | MEMT_CFG1_TBL16 |  |  |  |  |

| 0x12  | MEMT_CTL_1       | MEMT_CFG2_TBL1 | MEMT_CFG2_TBL2 |  | MEMT_CFG2_TBL16 |  |  |  |  |

| 0x13  | MEMT_CTL_2       | MEMT_CFG3_TBL1 | MEMT_CFG3_TBL2 |  | MEMT_CFG3_TBL16 |  |  |  |  |

| 0x14  | MEMT_CTL_3       | MEMT_CFG4_TBL1 | MEMT_CFG4_TBL2 |  | MEMT_CFG4_TBL16 |  |  |  |  |

| 0x15  | POLL_CYC_CNT     | MEMT_CFG5_TBL1 | MEMT_CFG5_TBL2 |  | MEMT_CFG5_TBL16 |  |  |  |  |

| 0x16  | POLL_CYC_CNT_    | MEMT_CFG6_TBL1 | MEMT_CFG6_TBL2 |  | MEMT_CFG6_TBL16 |  |  |  |  |

| 0x17  | RAM_CFG_TBL_C    | MEMT_CFG7_TBL1 | MEMT_CFG7_TBL2 |  | MEMT_CFG7_TBL16 |  |  |  |  |

| 0x18  | TBL_CRC_CHK_T    | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x19  | DIAG_REG_1       | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x1A  | DIAG_REG_2       | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x1B  | DIAG_REG_3       | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x1C  | Reserved         | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x1D  | Reserved         | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x1E  | Reserved         | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

| 0x1F  | Reserved         | Reserved       | Reserved       |  | Reserved        |  |  |  |  |

|  | Bank | indepe | ndent | registers |

|--|------|--------|-------|-----------|

|--|------|--------|-------|-----------|

Registers under bank select. Bank selection is password protected.

# 8.1 MEMT\_DATA\_1-16 (Address 0x00-0x0F, all banks)

Table 18: Measurement data register

| R-0 <sup>(1)</sup> | R-0   | R-0    | R-0  | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|--------------------|-----|-----|-----|-----|-----|-----|-------|--------|------|-----|-----|-----|-----|-----|-----|

|                    |     |     |     |     |     | ME  | ASURE | MENT[1 | 5:0] |     |     |     |     |     |     |

|                    | BIT | 15  |     |     | BI  | Г8  |       |        | BI   | Т 7 |     |     | BI  | Γ0  |     |

| Field             | Description                                                                                                                   |                                                          |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|

|                   | The number of bits of measured value depends on the accumulation setting programmed in the corresponding configuration table: |                                                          |  |  |  |  |  |  |

|                   | ACCU[1:0]                                                                                                                     | MEASUREMENT[15:0]                                        |  |  |  |  |  |  |

|                   | 00                                                                                                                            | MEAS[15:4],0000                                          |  |  |  |  |  |  |

|                   | 01                                                                                                                            | MEAS[15:3],000                                           |  |  |  |  |  |  |

|                   | 10 MEAS[15:2],00                                                                                                              |                                                          |  |  |  |  |  |  |

| MEASUREMENT[15:0] | 11                                                                                                                            | MEAS[15:1],0                                             |  |  |  |  |  |  |

|                   | Polling mode:                                                                                                                 |                                                          |  |  |  |  |  |  |

|                   | FIFO buffer used; newest value                                                                                                | e is stored at address 0; second-last at address 1, etc. |  |  |  |  |  |  |

|                   | Single mode:                                                                                                                  |                                                          |  |  |  |  |  |  |

|                   | Value is stored at the address corresponding to the measurement table (e.g. measurement table 5 at address 4).                |                                                          |  |  |  |  |  |  |

|                   | Continuous mode:                                                                                                              |                                                          |  |  |  |  |  |  |

|                   | Value is stored at the address corresponding to the measurement table                                                         |                                                          |  |  |  |  |  |  |

<sup>(1) [</sup>Bit type]-[power-on value] →R = Read only, RW = Read/write E.g. R-1 means read-only bit with power-on at 1

### 8.2 BANK\_SEL (Address 0x10, all banks)

Table 19: Bank select register

| RW-0 | RW-0             | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0      | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 |

|------|------------------|------|------|------|------|------|-----------|------|------|------|------|------|------|------|------|

|      | ACCESS WORD[7:0] |      |      |      |      |      | BANK[7:0] |      |      |      |      |      |      |      |      |

|      | BIT 15 BIT 8     |      |      |      |      | BI   | Γ7        |      |      | BI   | Τ 0  |      |      |      |      |

| Field            | Description                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCESS WORD[7:0] | Password to protect from accidental change of content.  Data is written into the bank selection bits only when this field is 0x5A.  A wrong password will deselect the bank. |

| BANK[7:0]        | Selected bank number (0 to 0x11),<br>e.g. 0 selects bank 0. 0x11 selects bank 17.                                                                                            |

At power up no bank is selected and only this register is accessible. If no bank is selected and an SPI is initiated to access other registers, then the NO\_BANK\_ACCESS flag will turn on in DIAG\_REG\_2.

# 8.3 MEMT\_SEQ (Address 0x11, bank 0)

Table 20: Measurement sequence register

| RW-0 | RW-0              | RW-0 | RW-0 | RW-0              | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 |

|------|-------------------|------|------|-------------------|------|------|------|------|------|------|------|------|------|------|------|

|      | MEMT_SEQ_EN[15:0] |      |      |                   |      |      |      |      |      |      |      |      |      |      |      |

|      | BIT               | 15   |      | BIT 8 BIT 7 BIT 0 |      |      |      |      |      | Τ 0  |      |      |      |      |      |

| Field             | Description                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MENT OF O FAMAS O | Each bit enables a table in a measurement sequence; bit 0 corresponds to Table 1, bit 15 to Table 16. Configuration registers for Table X are available at bank X. |

| MEMT_SEQ_EN[15:0] | The measurement sequence moves from LSB to MSB, starting from the bit position specified in MEMT_STRT_PTR bits in MEMT_CNTL_2 register.                            |

|                   | In single measurement mode the content of this register is ignored.                                                                                                |

# 8.4 MEMT\_CNTL\_1 (Address 0x12, bank 0)

Table 21: Measurement control register 1

| RW-0 | RW-0 | RW-0 | RW-0   | RW-0 | RW-0         | RW-0 | RW-0 | RW-0 | RW-0           | RW-0 | RW-0 | RW-0 | RW-0           | RW-0 | RW-0 |  |  |

|------|------|------|--------|------|--------------|------|------|------|----------------|------|------|------|----------------|------|------|--|--|

| 0    | 0    | RCC  | 0[1:0] |      | CONTROL[4:0] |      |      |      | POLL_TIME[2:0] |      |      |      | REFERENCE[3:0] |      |      |  |  |

|      | ВІТ  | 15   |        |      | BIT 8        |      |      |      | BI             | Γ7   |      |      | ВІ             | Τ0   |      |  |  |

| Field          | Desc     | ription                                               |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|----------------|----------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                |          | lator frequency tuning.<br>setting is only applicable | when RCO_EN is set                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                | RCO      | [1:0]                                                 | Frequency                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RCO[1:0]       | 00       |                                                       | 4MHz + 80KHz                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                | 01       |                                                       | 4MHz + 160KHz                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                | 10       |                                                       | 4MHz - 80KHz                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                | 11       |                                                       | 4MHz - 160KHz                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                | Chip     | control settings                                      |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                | Bit Name |                                                       | Description                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                | 4        | INFINITE_POLLING                                      | 0 – Polling cycle counter is active. After each polling sequence the counter is decremented. Polling cycle will run until the counter becomes '0'. The counter status can be checked in the POLL_CYC_CNT_STS register.  1 – Polling cycle will run indefinitely. The polling cycle counter is not decremented. |  |  |  |  |  |

| CONTROL[4:0]   | 3        | CLEAR_MEMORY                                          | Clear measurement memory in polling mode.  0 – Previous measurement data is retained in memory.  Once measurement starts the corresponding locations will be overwritten.  1 – Clears measurement data from memory before starting polling. (Default)                                                          |  |  |  |  |  |

|                | 2        | DC_LPF_RESET                                          | Reset the DC/LPF between measurements 0 – Disabled. 1 – Enabled. (Default)                                                                                                                                                                                                                                     |  |  |  |  |  |

|                | 1        | CSN_PU                                                | Enable internal CSN pull up resister  0 – Pull up connected (Default)  1 – No pull up.                                                                                                                                                                                                                         |  |  |  |  |  |

|                | 0        | RCO_EN                                                | Enables oscillator control by RCO                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                | Pollin   | ng time selection (typical                            | value)                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                | POLI     | TIME[2:0]                                             | Time (ms)                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| POLL_TIME[2:0] | 000      |                                                       | 12                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                | 001      |                                                       | 16                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                | 010      |                                                       | 20                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Field          | Description                 |                               |

|----------------|-----------------------------|-------------------------------|

|                | 011                         | 28                            |

|                | 100                         | 36                            |

|                | 101                         | 48                            |

|                | 110                         | 64                            |

|                | 111                         | 128                           |

|                | Internal reference capacita | nce selection (typical value) |

|                | REFERENCE[3:0]              | Ref cap (pf)                  |

|                | 0000                        | -                             |

|                | 0001                        | 2                             |

|                | 0010                        | 4                             |

|                | 0011                        | 6                             |

|                | 0100                        | 8                             |

|                | 0101                        | 10                            |

| REFERENCE[3:0] | 0110                        | 12                            |

| REFERENCE[3.0] | 0111                        | 14                            |

|                | 1000                        | 16                            |

|                | 1001                        | 18                            |

|                | 1010                        | 20                            |

|                | 1011                        | 22                            |

|                | 1100                        | 24                            |

|                | 1101                        | 26                            |

|                | 1110                        | 28                            |

|                | 1111                        | 30                            |

# 8.5 MEMT\_CNTL\_2 (Address 0x13, bank 0)

Table 22: Measurement control register 2

| RW-0     | RW-0 | RW-0 | RW-0              | RW-0 | RW-0 | R-0 | R-0 | R-0 | R-0 |

|------|------|------|------|------|------|----------|------|------|-------------------|------|------|-----|-----|-----|-----|

| 0    | 0    | 0    | 0    |      | COMM | AND[3:0] |      |      | MEMT_CUR_PTR[3:0] |      |      |     |     |     |     |

|      | BIT  | Г 15 |      |      | ВІ   | T 8      |      |      | BIT 0             |      |      |     |     |     |     |

| Field              | Description                                                                                   |                  |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | Measurement or                                                                                | diagnostic mode. |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                    | COMMAND[3:0]                                                                                  | Name             | Description                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                    | 0000                                                                                          | NOP              | No operation will be performed.                                                                                                                                                                                                      |  |  |  |  |  |  |

|                    |                                                                                               |                  | Stop current measurement or trigger generation  Single mode: Measurement is stopped after current measurement is finished.                                                                                                           |  |  |  |  |  |  |

|                    | 0001                                                                                          | STOP             | <b>Polling mode:</b> Measurement is stopped after completing all measurements defined in MEMT_SEQ register.                                                                                                                          |  |  |  |  |  |  |

|                    |                                                                                               |                  | Continuous mode: Measurement is stopped after current measurement.                                                                                                                                                                   |  |  |  |  |  |  |

|                    | 0010                                                                                          | CLEAR_NOT_INIT   | Clear the NOT_INIT flag in the diagnostic register.                                                                                                                                                                                  |  |  |  |  |  |  |

|                    | 0011                                                                                          | INIT_MODE        | Configuration and control registers can be written exclusively in this mode.                                                                                                                                                         |  |  |  |  |  |  |

| COMMAND[3:0]       | 0100                                                                                          | POLLING_MODE     | The device performs the measurements in sequence, starting from the table pointed by MEMT_STRT_PTR and for tables enabled in MEMT_SEQ_EN; then it goes into power saving mode according to POLL_TIME setting; then the cycle repeats |  |  |  |  |  |  |

|                    | 0101                                                                                          | SINGLE_MODE      | The device performs one measurement, corresponding to the table pointed by MEMT_STRT_PTR                                                                                                                                             |  |  |  |  |  |  |

|                    | 0110                                                                                          | CONTINUOUS_MODE  | The device performs one measurement sequence, starting from the table pointed by MEMT_STRT_PTR and for tables enabled in MEMT_SEQ_EN                                                                                                 |  |  |  |  |  |  |