# Product Document

Published by ams OSRAM Group

## **Application Note**

AN000611

# NanEyeC MCU Interface

## **Single Ended Interface Mode for Standard MCUs**

v2-00 • 2022-May-20

## **Content Guide**

| 1                        | Introduction 3                  |

|--------------------------|---------------------------------|

| 2                        | NanEyeC SEIM 4                  |

| 2.1<br>2.2<br>2.3<br>2.4 | Single Ended Interface Mode     |

| 3                        | MCU-Based SEIM Implementation 7 |

| 3.1                      | MCU Interface7                  |

|                          |                                 |

| 3.2<br>3.3<br>3.4<br>3.5 | Example MCU Firmware Architecture8<br>Frame Capture Using 12-Bit SPI Interface8<br>Frame Capture Using 8-Bit SPI Interface9<br>Image Post-Processing and Control11 |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                        | Revision Information14                                                                                                                                             |

| 5                        | Legal Information15                                                                                                                                                |

## 1 Introduction

NanEyeC is a miniature image sensor with a resolution of 320 x 320 pixels designed for spaceconstrained vision applications. This application note focuses on the single ended interface mode (SEIM). It is designed to connect NanEyeC directly to standard microcontrollers via short connections and without the need for additional electronics.

Full details about the NanEyeC sensor and its configuration are provided in the NanEyeC datasheet DS000503.

## 2 NanEyeC SEIM

### 2.1 Single Ended Interface Mode

In addition to LVDS mode, NanEyeC supports a single ended interface mode (SEIM) allowing ams OSRAM customers to connect the image sensor to standard microcontroller units (MCU). The SEIM uses a clock line (SCLK), which is driven by the MCU, and a data line (SDAT) which is driven by the MCU during INTERFACE MODE periods and by NanEyeC during all other operation mode periods.

### 2.2 Word and Frame Format

Transmission between NanEyeC and an MCU is performed in 12-bit words. Such a 12-bit word is subsequently also referred to as a pixel period (PP).

A PP consisting of a start bit (1-bit) + data (10-bit) + stop bit (1-bit) as shown in Figure 1.

Figure 1:

Pixel Data Word Encoding SEIM

| # Rising<br>SCLK Edge | 0     | 1        | 2                    | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10   | 11 |

|-----------------------|-------|----------|----------------------|---|---|---|---|---|---|---|------|----|

| Function              | Start | Pixel Da | Pixel Data (10 bits) |   |   |   |   |   |   |   | Stop |    |

| Content               | 1     | MSB      |                      |   |   |   |   |   |   |   | LSB  | 0  |

A frame consist of 320 lines. Each line starts with 8 training PPs (cp. Figure 2) followed by 320 pixel data PPs (cp. Figure 1). Each frame is terminated by 8 end of frame PPs (EOF; see Figure 3). Hence, a frame transmitted by NanEyeC consists of 320 (lines) x 328 PPs (line data) + 8 PPs (EOF).

Figure 2:

Training Word Encoding SEIM (0x555)

| # Rising<br>SCLK Edge | 0     | 1        | 2                          | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10   | 11 |

|-----------------------|-------|----------|----------------------------|---|---|---|---|---|---|---|------|----|

| Function              | Start | Training | Training Pattern (10 bits) |   |   |   |   |   |   |   | Stop |    |

| Content               | 0     | 1        | 0                          | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0    | 1  |

#### Figure 3:

End Of Frame Word Encoding SEIM (0x000)

| # Rising<br>SCLK Edge | 0     | 1        | 2                              | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10   | 11 |

|-----------------------|-------|----------|--------------------------------|---|---|---|---|---|---|---|------|----|

| Function              | Start | End of F | End of Frame Pattern (10 bits) |   |   |   |   |   |   |   | Stop |    |

| Content               | 0     | 0        | 0                              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0  |

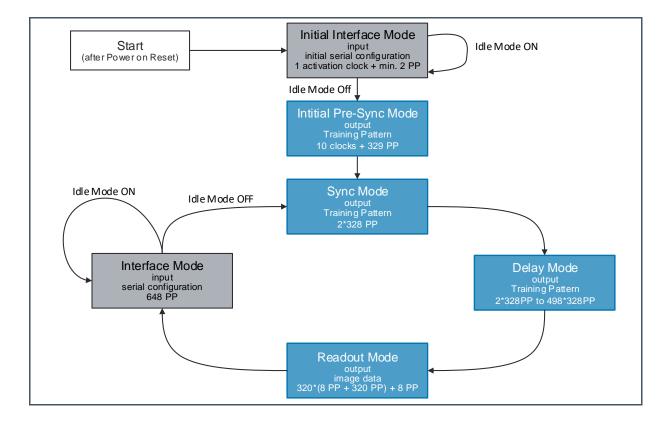

### 2.3 Sequence of Operation

As shown in Figure 4, each frame is preceded by an INTERFACE MODE period (648 PPs), a SYNC MODE period of 2 x 328 PPs and a DELAY MODE period of [2 to 498] x 328 PPs. An exception is the first frame after power-on reset. This frame is not preceded with a full INTERFACE MODE period but with a shorter, INITIAL INTERFACE MODE period followed by an INITIAL PRE-SYNC MODE.

Operation Sequence Modes (as shown in Figure 4):

- INITIAL INTERFACE MODE consists of a single clock and a minimum of 2 PPs. The 2 PPs are used to write to NanEyeC register CONFIGURATION\_1 (enable SEIM, disable IDLE mode, and other optional settings). Once IDLE mode is disabled, NanEyeC transitions to INITIAL PRE-SYNC MODE.

- **INITIAL PRE-SYNC MODE** consists of 10 clock periods plus 329 PPs. During INITIAL PRE-SYNC MODE, a fixed pattern is transmitted where one PP reads as 0xAAA.

- **INTERFACE MODE** consists of 648 PPs. Interface mode is used to write settings to the two NanEyeM registers. Register writes must not be performed in the last PP of interface mode!

- **SYNC MODE** consists of 2 x 328 = 656 PPs. During SYNC MODE, NanEyeC transmits a fixed training pattern of 0x555 (cp. Figure 2). Only for the first frame after power-on reset the pattern 0xAAA is transmitted instead.

- **DELAY MODE** increases exposure and frame rate by adding a delay ranging from a minimum of 2 x 328 PPs up to 498 x 328 PPs prior to frame readout. Note that including the minimum delay of 2 x 328 PPs in the operation sequence is mandatory.

- **READOUT MODE** is the period where NanEyeC transmits actual pixel data. Data transmission consists of 320 lines where each line starts with 8 PPs of training pattern (8 x 0x555) followed by 320 PP of pixel data. Note that the training pattern for the first line of the first frame after power-on reset is 0xAAA instead of 0x555.

- INTERFACE MODE consists of 648 PPs. Interface mode is used to write settings to the two NanEyeC registers.

#### Attention

Register writes must not be performed in the last PP of the INTERFACE MODE!

#### Figure 4: Sequence Of Operation

### 2.4 NanEyeC Register Access

NanEyeC provides two write-only configuration registers which can be written during the INITIAL INTERFACE MODE and the normal INTERFACE MODE. A register write is performed as a 24-bit (2PP) write operation by the MCU. The content of the register update packet is structure as shown in Figure 5.

Figure 5: Register Update Sequence

| # Rising<br>SCLK Edge | 0           | 1 | 2 | 3                | 4 | 5 | 6                          | 7   | 8 |  | 21 | 22  | 23 |

|-----------------------|-------------|---|---|------------------|---|---|----------------------------|-----|---|--|----|-----|----|

| Function              | Update Code |   |   | Register Address |   |   | Register Content (16 bits) |     |   |  |    | End |    |

| Content               | 1           | 0 | 0 | 1                | 0 | 0 | x                          | MSB |   |  |    | LSB | 0  |

For a detailed description of the NanEyeC register settings please refer to the NanEyeC datasheet DS000503. The most important actions for SEIM mode (applied during INITIAL INTERFACE MODE) are setting the output\_mode[0] from LVDS (default) to SEIM and to disable idle\_mode[0]. Both bits are located in the register **CONFIGURATION\_1**.

## am

## **3 MCU-Based SEIM Implementation**

### 3.1 MCU Interface

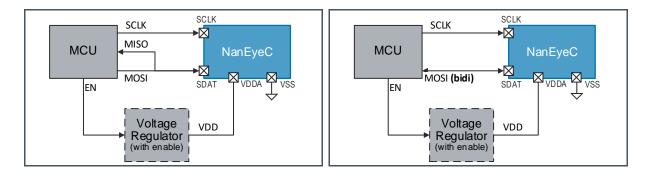

To capture frames efficiently with a standard MCU, using a hardware peripheral is recommended instead of bit banging. A widely available MCU interface suitable for NanEyeC is the Serial Peripheral Interface (SPI). In contrast to typical SPI configurations, NanEyeM does not have a chip select (CS) line. The absence of a CS line means that NanEyeC cannot easily share an SPI bus with other SPI peripherals. This is only possible if there is an auxiliary mechanism to disconnect NanEyeC from the SPI bus by, e.g. shutting down NanEyeC using an MCU-controlled power supply.

In a basic SPI configuration, the bidirectional SDAT data pin of NanEyeC is connected to both the SPI "master out / slave in" (MOSI) pin and the "master in / slave out" (MISO) pin (see Figure 6). In this configuration, it is up to the MCU to ensure that no data is sent via the MCU's MOSI pin while NanEyeC is transmitting data (and the MCU is receiving this data on the MISO pin). The actual implementation of this approach depends on the specific MCU used. Some MCU systems natively support a "3 wire"<sup>1</sup> (half duplex) SPI mode where the MOSI line supports bidirectional transmission. In such a configuration, the MISO line remains unused. Figure 7 shows this approach.

To reduce MCU load and make data transfers as efficient as possible, it is strongly advised to select an MCU which provides DMA engines serving the SPI peripheral. Moreover, some MCUs support 12-bit SPI transfers exactly matching the size of a NanEyeC pixel period. In contrast to 8-bit transfers, this slightly reduces MCU load for data re-alignment after capture.

Figure 6:

SPI Interconnection From MCU To NanEyeC With Separate, Selectively Activated MISO And MOSI Pins Figure 7: "3 Wire" SPI Interconnection From MCU To NanEyeC

<sup>1</sup> The term "3 wire" refers to CS, SCLK and MOSI lines. In case of NanEyeC, where no CS line is used, this effectively only 2 wires are used for communication.

## amu

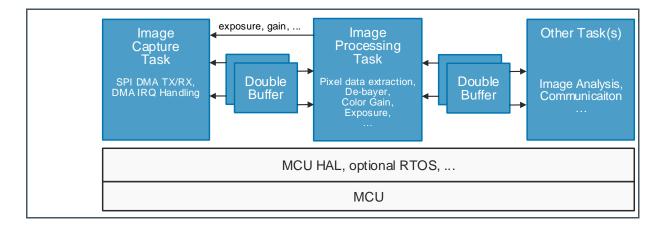

### 3.2 Example MCU Firmware Architecture

For efficient image capturing it is important to consider a few architectural aspects when designing the firmware. Figure 8 shows an example firmware architecture. A key aspect for continuous, high-framerate image delivery is that the image capturing task uses DMA transfers for image acquisition and hence offloading the MCU. To enable continuous capture, a double (or multi) buffer structure is required for transferring captured image data from the capture to the processing task. In the image processing task the captured data is then post processed. Specifically, the following steps need to be performed:

- Remove the 8 training words from each captured image row

- Remove start and stop bits from each pixel

- Optionally reduce the 10-bit pixel data to 8-bit (depending on the application requirements)

- Apply pre-color gain

- Apply de-bayering

- Adjust image exposure

#### Figure 8: Example Firmware Architecture

## 3.3 Frame Capture Using 12-Bit SPI Interface

If the MCU supports 12-bit SPI transfers, this mode is recommended for image capturing. 12-bit words from NanEyeC are then stored in 16-bit words in MCU memory. The capture sequence is then as follows:

```

// !! IMPORTANT !!

// In this example, an SPI word (i.e., a word sent/read on the

// bus by the spi_ functions) has a length 12 bits.

// after power-on reset NanEyeC is in IDLE MODE

spi_GenClocks(1); // generate a single clock for activation

spi_WriteWords(reg0_val, 2); // first 2 PP of INITIAL INTERFACE MODE

```

```

8

spi WriteWords(reg1 val, 2); // second 2 PP of INITIAL INTERFACE MODE

9

wait (10us); // wait for IDLE start-up (longer times are also possible)

spi_GenClocks(10); // generate 10 alignment clocks (before first frame only)

10

spi ReadWords DMA(329); // INITIAL PRE-SYNC MODE (read and ignore)

11

12

spi_ReadWords_DMA(656); // SYNC MODE (read and ignore)

spi_ReadWords_DMA(2*328);

// DELAY MODE (can be extended to 498x328PP)

13

spi ReadWords DMA(320*328); // READOUT mode first image (read and ignore)

14

// end of frame (read and ignore)

15

spi ReadWords DMA(8);

16

17

// main capture loop

18

while(True) {

spi_WriteWords(reg0_val, 2); // first 2 PP of INTERFACE MODE

19

spi_WriteWords(reg1_val, 2); // second 2 PP of INTERFACE MODE

20

spi_WriteWords(0x0, 644);

21

// rest of INTERFACE MODE (648 - 4PP)

spi ReadWords DMA(4*328);

// SNYC and DELAY MODEs (read and ignore)

22

img = spi ReadWords DMA(320*328); // READOUT MODE

23

// end of frame (read and ignore)

24

spi_ReadWords_DMA(8);

25

send_ImgToProcessingTask(img);

26

}

```

Start and stop bits for a pixel need to be masked/shifted out in a separate post-processing step.

#### DMA Transfer Size

The DMA controllers of many MCUs have the limitation that the DMA counter is only 16 bits. Therefore, the NanEyeC pixel data cannot be read in a single DMA transfer but has to be split up into several transfers. Starting the next DMA transfer takes a small amount of time resulting in a small gap in the SPI clock. This clock gap results in an effect where the pixels of the next DMA transfer might be overexposed. Therefore, it is recommended to align DMA transfer boundaries with the end of an image row and, if needed, reconstruct the values of overexposed pixels based on the values of neighbor pixels using averaging.

#### High-Speed Clocks

For high SPI clock frequencies above 40 MHz the NanEyeM data signal might not be stable enough at the rising edge of the clock. In these situations, it is recommended to sample at the signal at the falling edge of the clock (i.e., SPI CPHA to the second clock edge).

### 3.4 Frame Capture Using 8-Bit SPI Interface

If only 8-bit SPI transfers are supported by the MCU, 2PPs are transferred into memory as a unit of 3 bytes, which need to be separated into two distinct pixel values in a separate post-processing step. The capture sequence is then as follows:

## amu

```

1

// !! IMPORTANT !!

// In this example, an SPI word (i.e., a word sent/read on the

2

3

// bus by the spi_ functions) has a length 8 bits.

4

// after power-on reset NanEyeC is in IDLE MODE

5

spi_GenClocks(1); // generate a single clock for activation

6

spi WriteWords(reg0 val, 3); // first 2 PP of INITIAL INTERFACE MODE

7

spi WriteWords(reg1 val, 3); // second 2 PP of INITIAL INTERFACE MODE

8

9

wait (10us); // wait for IDLE start-up (longer times are also possible)

spi_GenClocks(10); // generate 10 alignment clocks (before first frame only)

10

spi GenClocks(12); // first PP of INITIAL PRE-SYNC MODE (read and ignore)

11

spi_ReadWords_DMA(492); // INITIAL PRE-SYNC MODE (read and ignore)

12

13

spi_ReadWords_DMA(984); // SYNC MODE (read and ignore)

spi_ReadWords_DMA(984); // DELAY MODE (can be extended to 498x328PP)

14

spi_ReadWords_DMA(320*492); // READOUT mode first image (read and ignore)

15

spi_ReadWords_DMA(12); // end of frame (read and ignore)

16

17

18

// main capture loop

19

while(True) {

spi_WriteWords(reg0_val, 3); // first 2 PP of INTERFACE MODE

20

spi_WriteWords(reg1_val, 3); // second 2 PP of INTERFACE MODE

21

spi_WriteWords(0x0, 966); // rest of INTERFACE MODE (648 - 4PP)

22

23

spi_ReadWords_DMA(4*492); // SNYC and DELAY MODEs (read and ignore)

img = spi_ReadWords_DMA(320*492); // READOUT MODE

24

// end of frame (read and ignore)

25

spi ReadWords DMA(12);

send_ImgToProcessingTask(img);

26

27

}

```

Start and stop bits for a pixel need to be masked/shifted out in a separate post-processing step.

Compared to the 12-bit variant, with 8-bit SPI word size all transfer counts are multiplied by 1.5. Since the INITIAL PRE-SYNC MODE consists of an uneven number of PPs, this would require the transfer of a half-word (4-bit) in the SPI bus. To overcome this issue it is recommended to clock in the first PP of the INITIAL PRE-SYNC MODE using bit banging (line 10 in the listing above).

Data read from the sensor is stored in memory such that two pixels are stored in three consecutive bytes. In a post-processing step the start and stop bits of the pixels have to be removed and the pixels have to be separated. A corresponding code snippet is show below:

```

1 U8 *data; // array with captured pixel data

2 U16 first_pixel = ((data[0] << 3) & 0x3F8) | (data[1] >> 5)

3 U16 second_pixel = ((data[1] << 7) & 0x380) | (data[2] >> 1)

```

### 3.5 Image Post-Processing and Control

#### 3.5.1 Pre-Color Gain

Pre-color gain changes pixel values after capture (and before color reconstruction). Adjustment values for red, green and blue pixels can be defined separately. The raw pixel values are the multiplied with these adjustment values resulting in either an attenuation or an amplification of the color component.

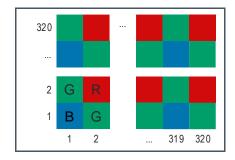

#### 3.5.2 De-Bayering

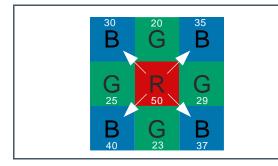

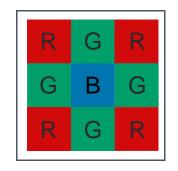

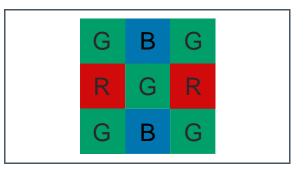

For de-bayering, bilinear color reconstruction can be applied. This generates a color image from the raw image captured from the sensor Figure 9 shows the color filter pattern used for the sensor where each individual pixel is either red, green or blue. The other two color components have to be reconstructed form neighboring pixels.

Figure 9: Color Filter Pattern

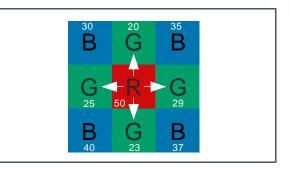

For red pixels, their green pixel value is the mean of the four surrounding green pixels (horizontal and vertical). The blue pixel value is the mean of the surrounding blue pixels (diagonal). This approach is shown in Figure 10 and Figure 11. For this example, the RGB value of the pixel is (50, 24, 35).

Figure 10: Blue Value Reconstruction For Red Pixel Figure 11: Green Value Reconstruction For Red Pixel

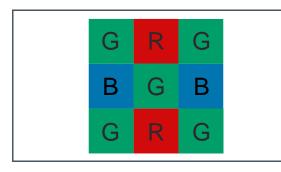

For blue pixels the computation of red and green is done in an analog way (mean of green and red neighbors as show in Figure 12

Figure 12: Blue Pixel Neighborhood

Finally, in case of green pixels the missing blue and red components are not computed from four but only two neighboring pixels, namely the two horizontal/vertical red/blue pixels as shown in Figure 13 and Figure 14.

Figure 13: Green Pixel Neighborhood – Case 1

### 3.5.3 Exposure Control

Image exposure is controlled be the following settings:

- Rows in reset

- Rows delay

- Gain (Ramp and CDS)

A simple approach to adjust image exposure is to compute the histogram of the image, determine the mean and assess its location within the histogram. If it is left of the histogram's center, the exposure of the image needs to be increased by:

- Decreasing the rows in reset and/or

- Increasing the rows delay and/or

• Increasing the gain settings.

Vice versa if the mean is right of the histogram's center, the exposure needs to be decreases by:

- Increasing the rows in reset and/or

- Decreasing the rows delay and/or

- Decreasing the gain settings.

New rows in reset, rows delay and gain settings can be performed via NanEyeC registers which can be written by the host during INTERFACE MODE. Be aware that changing the rows delay setting also means that the amount of training pattern read from the sensor before the actual pixel data increases.

## **4** Revision Information

| Changes from previous version to current revision v2-00 | Page  |

|---------------------------------------------------------|-------|

| Changed Security Class from CONFIDENTIAL to PUBLIC      |       |

| De-Bayering Section Figures Updated                     | 11-12 |

• Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

• Correction of typographical errors is not explicitly mentioned.

## **5 Legal Information**

#### **Copyrights & Disclaimer**

Copyright ams-OSRAM AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Information in this document is believed to be accurate and reliable. However, ams-OSRAM AG does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Applications that are described herein are for illustrative purposes only. ams-OSRAM AG makes no representation or warranty that such applications will be appropriate for the specified use without further testing or modification. ams-OSRAM AG takes no responsibility for the design, operation and testing of the applications and end-products as well as assistance with the applications or end-product designs when using ams-OSRAM AG products. ams-OSRAM AG is not liable for the suitability and fit of ams-OSRAM AG products in applications and end-product planned.

ams-OSRAM AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data or applications described herein. No obligation or liability to recipient or any third party shall arise or flow out of ams-OSRAM AG rendering of technical or other services.

ams-OSRAM AG reserves the right to change information in this document at any time and without notice.

#### **RoHS Compliant & ams Green Statement**

**RoHS Compliant:** The term RoHS compliant means that ams-OSRAM AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories plus additional 4 substance categories (per amendment EU 2015/863), including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

ams Green (RoHS compliant and no Sb/Br/Cl): ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material) and do not contain Chlorine (Cl not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams-OSRAM AG knowledge and belief as of the date that it is provided. ams-OSRAM AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams-OSRAM AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams-OSRAM AG and ams-OSRAM AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

| Headquarters            | Please visit our website at www.ams.com                                       |

|-------------------------|-------------------------------------------------------------------------------|

| ams-OSRAM AG            | Buy our products or get free samples online at www.ams.com/Products           |

| Tobelbader Strasse 30   | Technical Support is available at www.ams.com/Technical-Support               |

| 8141 Premstaetten       | Provide feedback about this document at www.ams.com/Document-Feedback         |

| Austria, Europe         | For sales offices, distributors and representatives go to www.ams.com/Contact |

| Tel: +43 (0) 3136 500 0 | For further information and requests, e-mail us at ams_sales@ams.com          |