# **amu** AS1163

# **Datasheet**

# **Table of contents**

| 1 | Ger | neral description         | 3  |

|---|-----|---------------------------|----|

|   | 1.1 | Key benefits & features   | 3  |

|   | 1.2 | Applications              | 4  |

|   | 1.3 | Use case overview         | 5  |

|   | 1.4 | Block diagram             | 8  |

| 2 | Ord | dering information        | 9  |

| 3 | Pin | assignment                | 10 |

|   | 3.1 | Pin diagram               | 10 |

|   | 3.2 | Pin description           | 11 |

| 4 | Abs | solute maximum ratings    | 13 |

| 5 | Ele | ctrical characteristics   | 14 |

|   | 5.1 | Power supply              | 18 |

|   | 5.2 | Startup sequence          | 18 |

| 6 | Pac | ckage drawings & markings | 19 |

| 7 | Тар | oe & reel information     | 20 |

| 8 | Rev | vision information        | 21 |

| 9 | Leg | gal information           | 22 |

## **AS1163 SAID - Standalone intelligent driver**

## 1 General description

AS1163 is a mixed signal silicon device optimized for dynamic lighting applications.

The basic purpose of AS1163 is to drive 9 LEDs organized in 3 channel triplets (RGB) with an independent PWM dimming dynamic range up to 16 bits.

AS1163 is often addressed with a different name: "SAID", an acronym, which stands for Stand-Alone Intelligent Driver.

Daisy chain configurations of multiple AS1163 devices will enable cost effective implementation of complex dynamic lighting effects.

AS1163 will support single layer slim PCB designs.

The communication protocol supported by AS1163 is Open System Protocol (OSP), which makes the SAID fully compatible with the ams OSRAM OSIRE E3731i. AS1163 will support additional features such as I<sup>2</sup>C gateway, parallel connection, power-rail feedback, analog readout.

Each AS1163 device in the chain will be usable by a MCU to read and write an external I<sup>2</sup>C device, e.g. EEPROM, temperature sensor, Ambient Light Sensor.

AS1163 is with Functional Safety QM and supports to achieve ASIL-B on system level.

### 1.1 Key benefits & features

The benefits and features of AS1163, SAID - Standalone intelligent driver are listed below:

Table 1: Added value of using AS1163

| Benefits                     | Features                                                                                                                                    |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Cost effective system design | Single layer PCB                                                                                                                            |  |  |

| Slim layout                  | 3x RGB channels per IC                                                                                                                      |  |  |

| Sensing integration          | I <sup>2</sup> C gateway (compatible with 5V and tolerant for 3V3 and 1V8)                                                                  |  |  |

| Open system protocol         | <ul> <li>Auto-addressing 2.4 Mbit/s two-wire daisy chain protocol</li> <li>Up to 1000 nodes</li> <li>CRC protected communication</li> </ul> |  |  |

| Open system protocor         | CRC protected communication                                                                                                                 |  |  |

| Benefits                                                                               | Features                                                                                                                         |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Adjustable output current                                                              | 1.5, 3, 6, 12, 24, 48 mA                                                                                                         |

| Configurable output power                                                              | Output clustering options (up to 288 mA)                                                                                         |

| Brightness adjustment                                                                  | 16-bit equivalent dynamic range when LSB dithering function is activated. 15-bit PWM engine @ 500 Hz 14-bit PWM engine @ 1000 Hz |

| <ul><li>Low EMI</li><li>Low power consumption</li><li>Reduced phantom effect</li></ul> | Enhanced driving mode (Dithering)                                                                                                |

| Star network implementation                                                            | External setting of parallel addressing (also called branching)                                                                  |

| Sync pin                                                                               | External HW sync for display application                                                                                         |

| Remote analog input for sensing                                                        | Integrated 10-bit ADC + MUX – range VDD – VDD-3.56 V                                                                             |

| Functional Safety                                                                      | QM (compliant with ASIL-B on system level)                                                                                       |

### 1.2 Applications

- Interior dynamic lighting effect

- Ambient lighting

- Functional lighting

- Exterior lighting (e.g. grill application)

- Roof lighting

- Smart surface

#### 1.3 Use case overview

In this section possible use cases of AS1163 are presented.

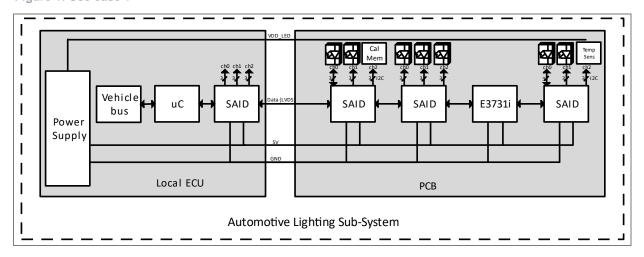

Figure 1: Use case 1

Figure 1 shows daisy chain using LVDS as local bus and supporting OSIRE E3731i and I<sup>2</sup>C device interfacing.

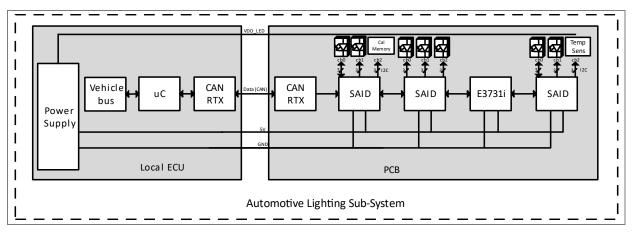

Figure 2: Use case 2

Figure 2 shows daisy chain using CAN bus and supporting OSIRE E3731i and I<sup>2</sup>C device interfacing.

MCU mode having Manchester downstream and data & clock upstream will produce communication error flags at parallel devices that are not addressed, while MCU - SPI mode supports parallel communication, given its symmetry in downstream and upstream flows.

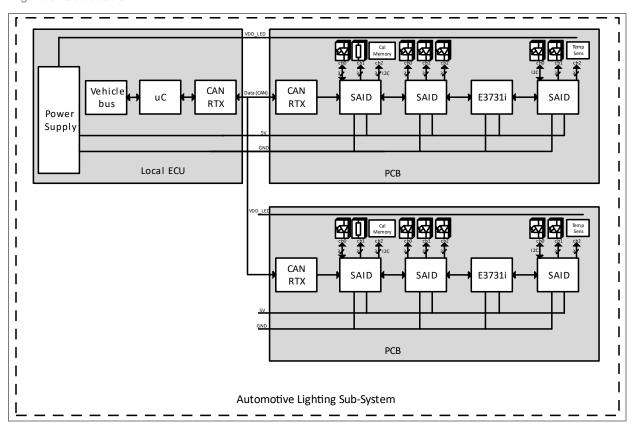

Figure 3: Use case 3

Figure 3 shows parallel connection of Daisy Chains using local CAN bus, supporting OSIRE RGBi and I<sup>2</sup>C device interfacing.

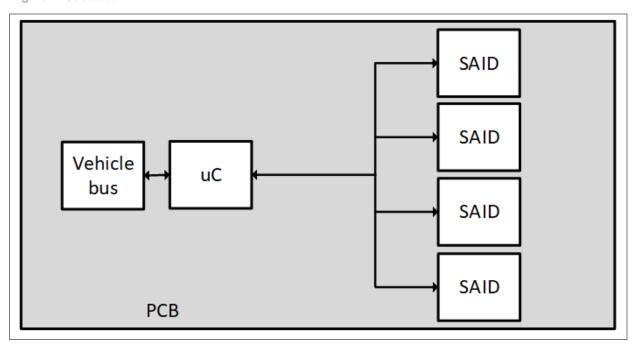

Parallel addressing (Figure 4) is fully supported with symmetrical communication modes, such as SPI-mode, LVDS mode, CAN mode.

Figure 4: Use case 4

Figure 4 shows parallel connection of SAID devices with direct MCU connection.

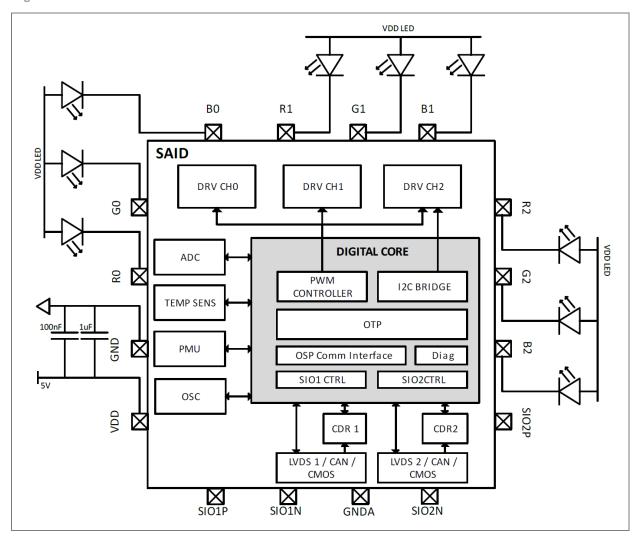

### 1.4 Block diagram

The functional blocks of this device are shown below:

Figure 5: Functional blocks of AS1163

# 2 Ordering information

| Ordering code | Package | Marking | Delivery form | Delivery quantity |

|---------------|---------|---------|---------------|-------------------|

| Q65113A6575   | QFN16   | AS1163  | Tape & reel   | 5k pcs/reel       |

| Q65113A9863   | QFN16   | AS1163  | Tape & reel   | 1k pcs/reel       |

# 3 Pin assignment

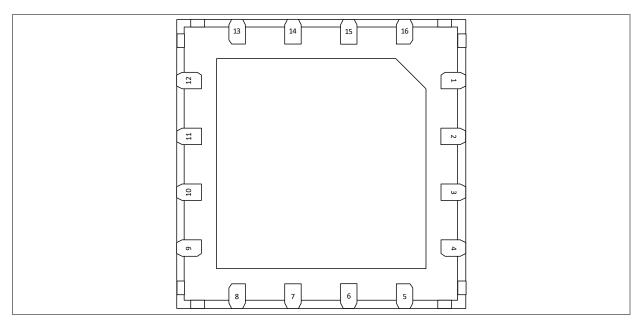

### 3.1 Pin diagram

Figure 6: Block diagram and pinout (package bottom view)

(1) The heat pad on bottom side is connected to the device substrate. It is recommended to connect the heat pad to GND or leave it floating, do not connect to any other signal.

### 3.2 Pin description

Table 2: Pin description of AS1163

| Pin number | Pin name | Pin type <sup>(1)</sup> | Description <sup>(2)</sup>                                             |

|------------|----------|-------------------------|------------------------------------------------------------------------|

| QFN 3x3 16 |          |                         |                                                                        |

| 1          | G0       | ANA                     | Driver 1 of channel 0 (Green)                                          |

| 2          | R0       | ANA                     | Driver 0 of channel 0 (Red)                                            |

| 3          | GNDP     | PWR                     | Power ground                                                           |

| 4          | VDD      | PWR                     | 5 V power supply                                                       |

| 5          | SIO1P    | ANA/DIO                 | Positive digital IO for SIO1 interface                                 |

| 6          | SIO1N    | ANA/DIO                 | Negative digital IO for SIO1 interface                                 |

| 7          | GNDA     | PWR                     | Analog ground                                                          |

| 8          | SIO2N    | ANA/DIO                 | Negative digital IO for SIO2 interface, test-bus                       |

| 9          | SIO2P    | ANA/DIO                 | Positive digital IO for SIO2 interface, test-bus                       |

| 10         | B2       | ANA                     | Driver 2 of channel 2 (Blue), also INT                                 |

| 11         | G2       | ANA                     | Driver 1 of channel 2 (Green), also SCL                                |

| 12         | R2       | ANA                     | Driver 0 of channel 2 (Red), also SDA                                  |

| 13         | B1       | ANA                     | Driver 2 of channel 1 (Blue), also SYNC                                |

| 14         | G1       | ANA                     | Driver 1 of channel 1 (Green), also for parallel address configuration |

| 15         | R1       | ANA                     | Driver 0 of channel 1 (Red), also for parallel address configuration   |

| 16         | В0       | ANA                     | Driver 2 of channel 0 (Blue)                                           |

(1) Explanation of abbreviations:

DIO Digital input and output

ANA Analog pin

PWR Power pin

(2) Pin name: R, G and B are only for naming purposes, not necessarily to be bound to red, green or blue color.

DRV\_BØ DRV\_R1 DRV\_G1 DRV\_B1 C7 IN #1 I.D 13 16 15 14 O . 12 DRV\_GØ DRV\_R2 11-14  ${\tt SAID\_V1p\emptyset}$  $\mathrm{DRV}\underline{\phantom{}}\mathrm{R}\emptyset$ DRV\_G2 9 3 18. 🕦 3  $1\emptyset$ 86 DRV\_B2 GNDP 4 9 SIO2\_P  $\nabla DD$ 0 0 0 5 6 8  $SI02_N$ SI01\_P SI01\_N GNDA

Figure 7: Pin arrangement (top view)

## 4 Absolute maximum ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3: Absolute maximum ratings of AS1163

| Symbol                             | Parameter                                     | Min                    | Max                       | Unit  | Comments                            |

|------------------------------------|-----------------------------------------------|------------------------|---------------------------|-------|-------------------------------------|

| Electrical p                       | parameters                                    |                        |                           |       |                                     |

| V <sub>DD</sub> / V <sub>GND</sub> | Supply voltage to ground                      | -0.3                   | 7                         | V     | Referenced to GND                   |

| V <sub>IN</sub>                    | Input pin voltage to ground                   | -0.3                   | V <sub>DD</sub> +0.3      | V     |                                     |

| I <sub>SCR</sub>                   | Input current (latch-up immunity)             | ±                      | 100                       | mA    | AEC-Q100-004                        |

| Continuous                         | s power dissipation (T <sub>A</sub> = 70 °C)  |                        |                           |       |                                     |

| P <sub>T</sub>                     | Continuous power dissipation                  |                        | 600                       | mW    |                                     |

| Continuous                         | s power dissipation (T <sub>A</sub> = 125 °C, | V <sub>OUT</sub> = 2.5 | V, R <sub>TH</sub> = 71.6 | °C/W) |                                     |

| P <sub>T</sub>                     | Continuous power dissipation                  |                        | 300                       | mW    |                                     |

| Electrostat                        | ic discharge                                  |                        |                           |       |                                     |

| ESD <sub>HBM</sub>                 | Electrostatic discharge HBM                   | =                      | ± 4                       | KV    | AEC-Q100-002                        |

| ESD <sub>CDM</sub>                 | Electrostatic discharge CDM                   | ±                      | 500                       | V     | AEC-Q100-011, ±750V for corner pins |

| Temperatu                          | re ranges and storage conditions              | 3                      |                           |       |                                     |

| T <sub>A</sub>                     | Operating ambient temperature                 | -40                    | 125                       | °C    |                                     |

| T <sub>J</sub>                     | Operating junction temperature                | -40                    | 150                       | °C    |                                     |

| $T_{STRG}$                         | Storage temperature range                     | -55                    | 150                       | °C    |                                     |

| T <sub>BODY</sub>                  | Package body temperature                      |                        | 260                       | °C    | IPC/JEDEC J-STD-020 <sup>(1)</sup>  |

| RH <sub>NC</sub>                   | Relative humidity (non-<br>condensing)        | 5                      | 85                        | %     |                                     |

| MSL                                | Moisture sensitivity level                    |                        | 3                         |       | ICP/JEDEC J-STD-033                 |

<sup>(1)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100 % Sn).

## 5 Electrical characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. Voltages are referred to the GNDA pin unless differently specified.

**Table 4: Electrical characteristics of AS1163**

| Symbol       | Parameter                                                                      | Conditions                                                                                                      | Min     | Тур     | Max     | Unit |

|--------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| Startup time |                                                                                |                                                                                                                 |         |         | 1       | ms   |

| VDD_com_stop | VDD communication<br>stop (stop of<br>communication when<br>VDD drops below)   |                                                                                                                 |         | 2.6     |         | V    |

| VDD          | Positive supply voltage                                                        |                                                                                                                 | 4.3     |         | 5.5     | V    |

| IDD          | Supply current                                                                 | All drivers at full current                                                                                     |         | 50      |         | mA   |

| IDD_sleep    | Sleep current                                                                  |                                                                                                                 |         | 1.6     |         | mA   |

| IDD_Dsleep   | Deep sleep current                                                             |                                                                                                                 |         | 1.5     |         | mA   |

| VLED_Head    | Min headroom LED driver                                                        | 1% current compression relative to 2.5V                                                                         |         | 600     |         | mV   |

| LED_Short    | LED short detection threshold                                                  |                                                                                                                 | VDD-1.8 | VDD-1.2 | VDD-0.5 | V    |

| LED_Open     | LED open detection threshold                                                   |                                                                                                                 | 50      | 250     | 550     | mV   |

| LED_Pers     | Minimum PWM duration and fault duration for LED_open / LED_Short functionality |                                                                                                                 |         | 27      |         | μs   |

| ILED_abs_acc | LED current absolute accuracy                                                  | Max ILED absolute driver accuracy. Over the whole temperature range and max current setting. Tested with VDD=5V | -8.5    |         | 8.5     | %    |

| Symbol         | Parameter                                      | Conditions                                                                                                                                     | Min                          | Тур   | Max | Unit   |

|----------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------|-----|--------|

| ILED_C2C_Mis   | LED channel to channel matching <sup>(1)</sup> | Max ILED Channel to Channel over the whole temperature range and max current setting. Tested with VDD=5V                                       | -5                           |       | 5   | %      |

| ILED_Mis       | LED channel current matching <sup>(2)</sup>    | Max ILED Driver<br>to Driver (same<br>channel). Over<br>the whole<br>temperature<br>range and max<br>current setting.<br>Tested with<br>VDD=5V | -2.5                         |       | 2.5 | %      |

| ILED_rise/fall | LED rising / falling edge                      | From 10 to 90%                                                                                                                                 |                              | 50    |     | ns     |

| LED Off        | LED Off current                                |                                                                                                                                                |                              | 3     |     | μA     |

| PWM_freq       | PWM freq. fast                                 |                                                                                                                                                |                              | 1.172 |     | kHz    |

| PWM_freq       | PWM freq. slow                                 |                                                                                                                                                |                              | 0.586 |     | kHz    |

| PWM_res        | PWM freq. fast                                 |                                                                                                                                                |                              | 14    |     | bit    |

| PWM_res        | PWM freq. slow                                 |                                                                                                                                                |                              | 15    |     | bit    |

| PWM_freq_acc   | PWM freq. accuracy                             |                                                                                                                                                | -5                           |       | 5   | %      |

| PWM_INL        |                                                |                                                                                                                                                |                              | 0.2   |     | LSB    |

| VDD_UV         | Under voltage threshold                        |                                                                                                                                                |                              | 4.15  |     | V      |

| VDD_UV_HYST    | Under voltage hysteresis                       |                                                                                                                                                |                              | 100   |     | mV     |

| VTH_Dig        | Valid digital input(3)                         |                                                                                                                                                | 0.5                          | 0.75  | 1.2 | V      |

| ADC_VREF1      |                                                |                                                                                                                                                |                              | 0.365 |     | V      |

| ADC_VREF2      |                                                |                                                                                                                                                |                              | 0.972 |     | V      |

| ADC_VREF       | Buffered ADC reference                         |                                                                                                                                                |                              | 1.340 |     | V      |

| ADC_OS         | ADC offset <sup>(4)</sup>                      | Vf meas.                                                                                                                                       | -2                           |       | 2   | LSB    |

| ADC_RANGE      | Typical input range,<br>Vf mode                | Vf meas.                                                                                                                                       | VDD -<br>8/3<br>ADC_V<br>REF |       | VDD | V      |

| ADC_GAIN       |                                                | Vf meas.                                                                                                                                       |                              | 3.494 |     | mV/LSB |

|                |                                                |                                                                                                                                                |                              |       |     |        |

| Symbol          | Parameter                                                                      | Conditions                                                    | Min     | Тур | Max     | Unit |

|-----------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|---------|-----|---------|------|

| ADC_GAIN_ERR    | Gain variation                                                                 | Vf meas,<br>referred to full-<br>scale. Tested<br>with VDD=5V | -1.12   |     | 1.12    | %    |

| ADC_DNL         | DNL                                                                            | Vf meas.<br>Valid for<br>Tj<125°C                             | -1      |     | 1       | LSB  |

| ADC_INL         | INL                                                                            | Vf meas.                                                      | -3      |     | 3       | LSB  |

| ADC_TSAMPLE     |                                                                                | Vf meas.                                                      |         | 1.6 |         | μs   |

| T_acc           | Temperature sensor accuracy                                                    | Room temp.                                                    | -8      |     | 8       | °C   |

| T_AMB           | Ambient temperature                                                            |                                                               | -40     |     | 125     | °C   |

| T_J             | Junction temperature                                                           |                                                               | -40     |     | 150     | °C   |

| Rth             | Thermal resistance from junction to ambient temperature                        |                                                               |         | 64  |         | °C/W |

| V_th_se_high    | Threshold on SIOx_x to detect communication mode (high)                        |                                                               | 2.85    |     | VDD+0.3 | V    |

| V_th_se_low     | Threshold on SIOx_x to detect communication mode (low)                         |                                                               | -0.3    |     | 0.7     | V    |

| V_SIOx_P/N(O,L) | Output low level for pin SIOx_P and SIOx_N for single-ended communication      | 10k Ohm load                                                  | 0       |     | 0.7     | V    |

| V_SIOx_P/N(O,H) | Output high level for pin SIOx_P and SIOx_N for single-ended communication     | 10k Ohm load                                                  | VDD-0.7 |     | VDD     | ٧    |

| F_com_mcu       | Allowed input data rate for communication in MCU mode. Tested with VDD=5V.     |                                                               | 2.23    | 2.4 | 2.62    | Mbps |

| DUTY_com_mcu    | Allowed input duty cycle in MCU mode. Tested with VDD=5V.                      |                                                               | 47.5    |     | 52.5    | %    |

| F_com_can       | Allowed input data rate for communication in CAN RTX mode. Tested with VDD=5V. |                                                               | 2.31    | 2.4 | 2.55    | Mbps |

| Symbol        | Parameter                                                     | Conditions                               | Min  | Тур | Max     | Unit |

|---------------|---------------------------------------------------------------|------------------------------------------|------|-----|---------|------|

| DUTY_com_can  | Allowed input duty cycle in CAN RTX mode. Tested with VDD=5V. |                                          | 40   |     | 55      | %    |

|               | Time between consecutive telegrams from MCU                   | Dependent on<br>length of daisy<br>chain | 8.3  |     |         | μs   |

| VIH_SE        | High level input voltage single ended communication           |                                          | 2.4  |     | VDD+0.3 | V    |

| VIL_SE        | Low level input voltage single ended communication            |                                          | -0.3 |     | 0.7     | V    |

| LVDS_VCM      | LVDS common mode voltage with active communication            |                                          |      | 1.2 |         | V    |

| LVDS_VDIFF    | LVDS differential voltage                                     |                                          |      | 300 |         | mV   |

| LVDS_VCM_IDLE | LVDS common mode voltage with no active communication         |                                          |      | 0   |         | V    |

| LVDS_RTERM    | LVDS termination resistance                                   | Included in the IC                       |      | 200 |         | Ohm  |

| LVDS_ITX      | LVDS current                                                  |                                          |      | 1.5 |         | mA   |

(1) Channel to channel relative accuracy is calculated with the following formulas:  $ILED\_C2C\_Mis(ch0\_x) = ((0.5*I(ch0\_x) - average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))* \\ average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))*100 \\ ILED\_C2C\_Mis(ch1\_x) = ((I(ch1\_x) - average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))* \\ average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))*100, \\ ILED\_C2C\_Mis(ch2\_x) = ((I(ch2\_x) - average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))* \\ average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch1\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch2\_RGB)))*100, \\ average(0.5*I(ch0\_RGB),I(ch2\_RGB)))*100, \\ averag$

#### Where:

- a) ILED\_C2C\_Mis(ch0\_x) refers to a general driver x inside channel 0, for example: ch0\_R refers to the R driver in channel 0. Similarly, for ILED\_C2C\_Mis(ch1\_x), ILED\_C2C\_Mis(ch2\_x).

- b) I(ch0\_x) refers to the high current level of a particular driver in channel 0. Similarly, for I(ch1\_x) and I(ch2\_x),

- c) I(ch0\_RGB) refers to the sum of the high current levels for the drivers belonging to channel 0. Similarly, for I(ch1\_RGB) and I(ch2\_RGB).

- (2) In-channel relative accuracy is calculated with the following formula: ILED\_Mis(chx\_y) = ((I(chx\_y) - average(I(chx\_RGB))) / average(I(chx\_RGB)))\*100

#### Where:

- a) ILED\_Mis(chx\_y) refers to a general driver y inside a general channel x, for example: ch0\_R refers to the R driver in channel 0.

- b) I(chx\_y) refers to the high current level of a general driver y in a general channel x.

- c) I(chx\_RGB) refers to the sum of the high current levels of all drivers belonging to a general channel x.

- (3) LED drivers can be used as receiving path for: I2C bridge, Sync pin, parallel address setting by external HW.

- (4) Relative accuracy. For absolute accuracy, calibration in applications is necessary.

#### 5.1 Power supply

For operating SAID a voltage supply VDD of typical 5 V is required. Each SAID can sink up to nominal 288 mA from the LEDs and the power delivery network needs to be sized accordingly.

Decoupling caps are recommended between VDD and GND, placed as close as possible to the device power pins.

Recommended values for these caps are:

- 1 µF elco capacity

- 100 nF high ESR capacitor

- VDD voltage up to 6 V

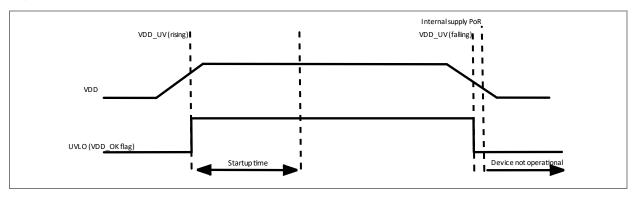

### 5.2 Startup sequence

The device starts-up with VDD overcoming the UVLO (undervoltage lockout) threshold. After the bandgap reference starts-up, the voltage regulator generates an internal voltage, VREG.

The internal blocks supplied by VREG (nominally 1.5 V) are reset until the supply reaches the POR\_N threshold. The RC oscillator is also enabled with POR\_N. In this state, for a trimmed device, the OTP is downloaded, and the trimming/configuration bits activated ( $\sim$ 200  $\mu$ s).

All internal blocks supplied by the external VDD supply start up after the supply reaches the UVLO threshold. At this point the communication interface and the led drivers are functional. Once the communication is enabled, also in case of an under-voltage event, the device does not lose functionality until an internal falling POR\_N event. The VDD\_OK flag signals that the VDD is above the VDD\_UV threshold.

Note: VREG, POR\_N are internal signals.

Figure 8: Startup sequence

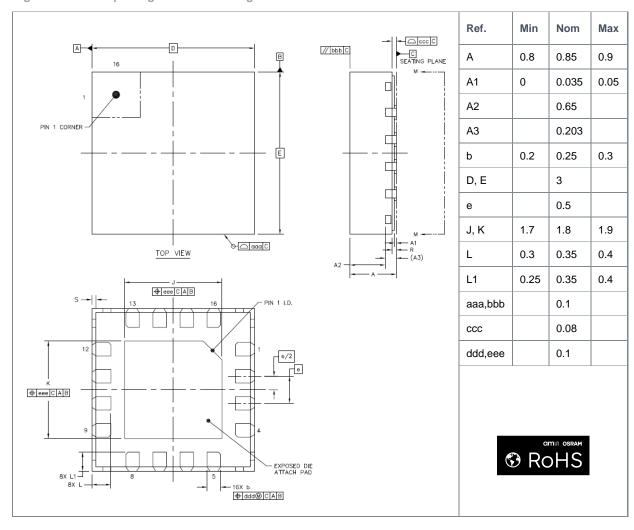

# 6 Package drawings & markings

Figure 9: AS1163 package outline drawing

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- (3) N is the total number of terminals.

- (4) This package contains no lead (Pb).

- (5) This drawing is subject to change without notice.

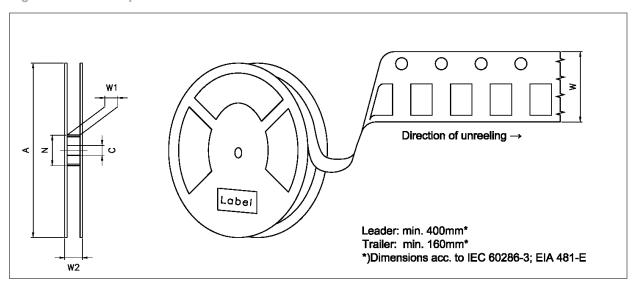

# 7 Tape & reel information

Figure 10: AS1163 tape and reel

Table 5: Reel dimensions

| Α      | W                | $N_{\text{min}}$ | <b>W</b> <sub>1</sub> | W <sub>2max</sub> | Pieces per PU |

|--------|------------------|------------------|-----------------------|-------------------|---------------|

| 330 mm | 12 + 0.3/-0.3 mm | 102 mm           | 12.8 mm               | 18.2 mm           | 5000          |

| 180 mm | 12 + 0.3/-0.3 mm | 60 mm            | 12.4 +2/-0 mm         | 18.4 mm max       | 1000          |

### 8 Revision information

| Document status       | Product status  | Definition                                                                                                                                                                                                                                              |

|-----------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview       | Pre-development | Information in this datasheet is based on product ideas in the planning phase of development. All specifications are design goals without any warranty and are subject to change without notice                                                         |

| Preliminary Datasheet | Pre-production  | Information in this datasheet is based on products in the design, validation or qualification phase of development. The performance and parameters shown in this document are preliminary without any warranty and are subject to change without notice |

| Datasheet             | Production      | Information in this datasheet is based on products in ramp-up to full production or full production which conform to specifications in accordance with the terms of ams-OSRAM AG standard warranty as given in the General Terms of Trade               |

#### Other definitions

Draft / Preliminary:

The draft / preliminary status of a document indicates that the content is still under internal review and subject to change without notice. ams-OSRAM AG does not give any warranties as to the accuracy or completeness of information included in a draft / preliminary version of a document and shall have no liability for the consequences of use of such information.

#### Short datasheet

A short datasheet is intended for quick reference only, it is an extract from a full datasheet with the same product number(s) and title. For detailed and full information always see the relevant full datasheet. In case of any inconsistency or conflict with the short datasheet, the full datasheet shall prevail.

#### Changes from previous version to current revision v1-00

**Page**

#### This short datasheet is derived from v1-00 of full datasheet

- Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

- Correction of typographical errors is not explicitly mentioned.

## 9 Legal information

#### Copyright & disclaimer

Copyright ams-OSRAM AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams-OSRAM AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams-OSRAM AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams-OSRAM AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams-OSRAM AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams-OSRAM AG for each application. This product is provided by ams-OSRAM AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams-OSRAM AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams-OSRAM AG rendering of technical or other services.

#### Product and functional safety devices/applications or medical devices/applications:

ams-OSRAM AG components are not developed, constructed or tested for the application as safety relevant component or for the application in medical devices. ams-OSRAM AG products are not qualified at module and system level for such application.

In case buyer – or customer supplied by buyer – considers using ams-OSRAM AG components in product safety devices/applications or medical devices/applications, buyer and/or customer has to inform the local sales partner of ams-OSRAM AG immediately and ams-OSRAM AG and buyer and/or customer will analyze and coordinate the customer-specific request between ams-OSRAM AG and buyer and/or customer.

#### ams OSRAM RoHS and REACH compliance statements for semiconductor products

RoHS compliant: The term "RoHS compliant" means that semiconductor products from ams OSRAM fully comply with current RoHS directives, and China RoHS. Our semiconductor products do not contain any chemicals for all 6 substance categories plus additional 4 substance categories (per amendment EU2015/863) above the defined threshold limit in the Annex II.

**REACH compliant:** Semiconductor products from ams OSRAM are free of Substances of Very High Concern (SVHC) according Article 33 of the REACH Regulation 2006/1907/EC; please refer to the Candidate List of Substances of ECHA here.

Important information: The information provided in this statement represents ams OSRAM knowledge and belief as of the date that it is provided. ams OSRAM bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. We are undertaking efforts to better integrate information from third parties. ams OSRAM has taken and will continue to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams OSRAM and its suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

Headquarters Please visit our website at ams-osram.com

ams-OSRAM AG For information about our products go to Products

Tobelbader Strasse 30 For technical support use our Technical Support Form

8141 Premstaetten For feedback about this document use **Document Feedback**

Austria, Europe For sales offices and branches go to Sales Offices / Branches

Tel: +43 (0) 3136 500 0 For distributors and sales representatives go to Channel Partners